# Cisco VCO/4K Card Technical Descriptions

Software Release 5.1 August 2000

**Corporate Headquarters**

Cisco Systems, Inc. 170 West Tasman Drive San Jose, CA 95134-1706 USA http://www.cisco.com Tel: 408 526-4000 800 553-NETS (6387) Fax: 408 526-4100

Customer Order Number: VCO4K-CARD-TD-DOC Part Number: 78-10751-03 THE SPECIFICATIONS AND INFORMATION REGARDING THE PRODUCTS IN THIS MANUAL ARE SUBJECT TO CHANGE WITHOUT NOTICE. ALL STATEMENTS, INFORMATION, AND RECOMMENDATIONS IN THIS MANUAL ARE BELIEVED TO BE ACCURATE BUT ARE PRESENTED WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED. USERS MUST TAKE FULL RESPONSIBILITY FOR THEIR APPLICATION OF ANY PRODUCTS.

THE SOFTWARE LICENSE AND LIMITED WARRANTY FOR THE ACCOMPANYING PRODUCT ARE SET FORTH IN THE INFORMATION PACKET THAT SHIPPED WITH THE PRODUCT AND ARE INCORPORATED HEREIN BY THIS REFERENCE. IF YOU ARE UNABLE TO LOCATE THE SOFTWARE LICENSE OR LIMITED WARRANTY, CONTACT YOUR CISCO REPRESENTATIVE FOR A COPY.

The following information is for FCC compliance of Class A devices: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio-frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case users will be required to correct the interference at their own expense.

The following information is for FCC compliance of Class B devices: The equipment described in this manual generates and may radiate radio-frequency energy. If it is not installed in accordance with Cisco's installation instructions, it may cause interference with radio and television reception. This equipment has been tested and found to comply with the limits for a Class B digital device in accordance with the specifications in part 15 of the FCC rules. These specifications are designed to provide reasonable protection against such interference in a residential installation. However, there is no guarantee that interference will not occur in a particular installation.

Modifying the equipment without Cisco's written authorization may result in the equipment no longer complying with FCC requirements for Class A or Class B digital devices. In that event, your right to use the equipment may be limited by FCC regulations, and you may be required to correct any interference to radio or television communications at your own expense.

You can determine whether your equipment is causing interference by turning it off. If the interference stops, it was probably caused by the Cisco equipment or one of its peripheral devices. If the equipment causes interference to radio or television reception, try to correct the interference by using one or more of the following measures:

• Turn the television or radio antenna until the interference stops.

· Move the equipment to one side or the other of the television or radio.

· Move the equipment farther away from the television or radio.

• Plug the equipment into an outlet that is on a different circuit from the television or radio. (That is, make certain the equipment and the television or radio are on circuits controlled by different circuit breakers or fuses.)

Modifications to this product not authorized by Cisco Systems, Inc. could void the FCC approval and negate your authority to operate the product.

The Cisco implementation of TCP header compression is an adaptation of a program developed by the University of California, Berkeley (UCB) as part of UCB's public domain version of the UNIX operating system. All rights reserved. Copyright © 1981, Regents of the University of California.

NOTWITHSTANDING ANY OTHER WARRANTY HEREIN, ALL DOCUMENT FILES AND SOFTWARE OF THESE SUPPLIERS ARE PROVIDED "AS IS" WITH ALL FAULTS. CISCO AND THE ABOVE-NAMED SUPPLIERS DISCLAIM ALL WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING, WITHOUT LIMITATION, THOSE OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT OR ARISING FROM A COURSE OF DEALING, USAGE, OR TRADE PRACTICE.

# IN NO EVENT SHALL CISCO OR ITS SUPPLIERS BE LIABLE FOR ANY INDIRECT, SPECIAL, CONSEQUENTIAL, OR INCIDENTAL DAMAGES, INCLUDING, WITHOUT LIMITATION, LOST PROFITS OR LOSS OR DAMAGE TO DATA ARISING OUT OF THE USE OR INABILITY TO USE THIS MANUAL, EVEN IF CISCO OR ITS SUPPLIERS HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Access Registrar, AccessPath, Any to Any, AtmDirector, Browse with Me, CCDA, CCDE, CCDP, CCIE, CCNA, CCNP, CCSI, CD-PAC, the Cisco logo, Cisco Certified Internetwork Expert logo, *CiscoLink*, the Cisco Management Connection logo, the Cisco NetWorks logo, the Cisco Powered Network logo, Cisco Systems Capital, the Cisco Systems Capital logo, Cisco Systems Networking Academy, the Cisco Systems Networking Academy logo, the Cisco Technologies logo, ConnectWay, Fast Step, FireRunner, Follow Me Browsing, FormShare, GigaStack, IGX, Intelligence in the Optical Core, Internet Quotient, IP/VC, Kernel Proxy, MGX, Natural Network Viewer, NetSonar, Network Registrar, the Networkers logo, *Packet*, PIX, Point and Click Internetworking, Policy Builder, Precept, RateMUX, ScriptShare, Secure Script, ServiceWay, Shop with Me, SlideCast, SMARTnet, SVX, *The Cell*, TrafficDirector, TransPath, ViewRunner, Virtual Loop Carrier System, Virtual Voice Line, VlanDirector, Voice LAN, Wavelength Router, Workgroup Director, and Workgroup Stack are trademarks; Changing the Way We Work, Live, Play, and Learn, Empowering the Internet Generation, The Internet Economy, and The New Internet Economy are service marks; and Aironet, ASIST, BPX, Catalyst, Cisco, Cisco IOS, the Cisco IS logo, Cisco Systems, the Cisco Systems logo, the Cisco Systems Cisco Press logo, Enterprise/Solver, EtherChannel, EtherSwitch, FastHub, FastLink, FastPAD, FastSwitch, GeoTel, IOS, IP/TV, IPX, LightStream, LightSwitch, MICA, NetRanger, Post-Routing, Pre-Routing, Registrar, StrataView Plus, Stratm, TeleRouter, and VCO are registered trademarks of Cisco Systems, Inc. or its affiliates in the U.S. and certain other countries. All other trademarks mentioned in this document are the property of their respective owners. The use of the word partner does not imply a partnership relationship between Cisco and any of its resellers. (0004R)

Cisco VCO/4K Card Technical Descriptions Copyright © 2000, Cisco Systems, Inc. All rights reserved.

#### VCO/4K Card Overview

| 1.0 INTRODUCTION                                                          | 1  |

|---------------------------------------------------------------------------|----|

| 2.0 CARD REMOVAL/REPLACEMENT PROCEDURES                                   | 1  |

| 2.1 Card Removal Procedure                                                | 2  |

| 2.2 Card Replacement Procedure                                            | 3  |

| 2.3 ICC I/O Module Removal Procedure                                      | 5  |

| 2.4 ICC I/O Module Replacement Procedure                                  | 5  |

| 3.0 CARD SPECIFICATIONS                                                   | 5  |

| 4.0 TROUBLESHOOTING                                                       | 6  |

| 4.1 System LogæError and Status Messages                                  | 6  |

| 4.2 Detecting and Correcting Analog Card Problems                         | 6  |

| 4.3 Service Circuit Test Utility                                          | 7  |

| 4.4 Test MF Receivers                                                     | 8  |

| 4.5 Detecting and Correcting T1,T1-E, E1, E1-PRI, and PRI/N Card Problems | 8  |

| 4.6 T1,T1-E, E1, E1-PRI, and PRI/N Card Maintenance States                | 9  |

| 4.7 Error Conditions Detected On Incoming Stream                          | 10 |

| 5.0 CISCO CONNECTION ONLINE                                               | 12 |

## Alarm Arbiter Card (AAC)with Alarm Interface Card (AIC)

| 1.0 GENERAL                          | 1  |

|--------------------------------------|----|

| 2.0 SPECIFICATIONS                   | 2  |

| 3.0 AAC CIRCUIT DESCRIPTION          | 3  |

| 3.1 Watchdog Timer Circuit           | 4  |

| 3.2 Switching From Active To Standby | 4  |

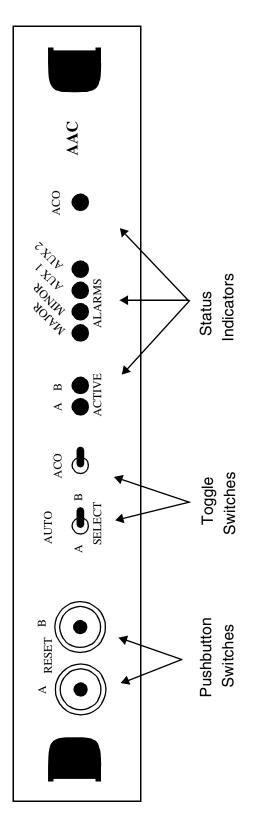

| 3.3 Front Panel Switches             | 5  |

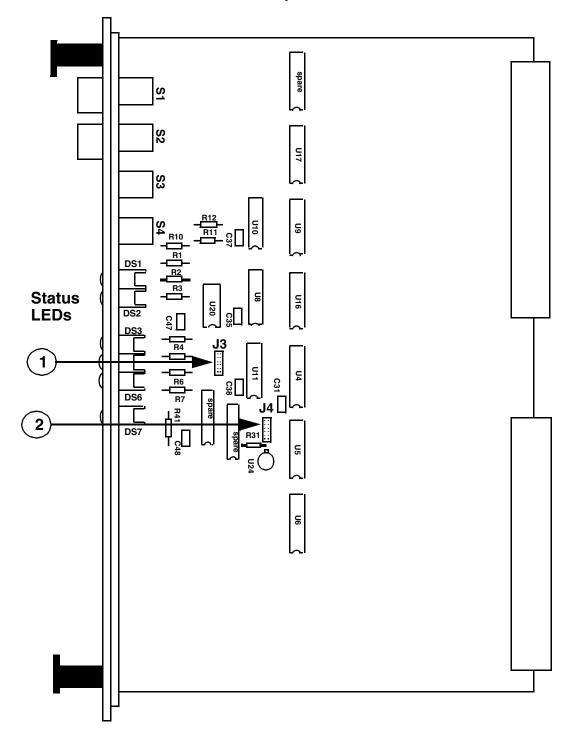

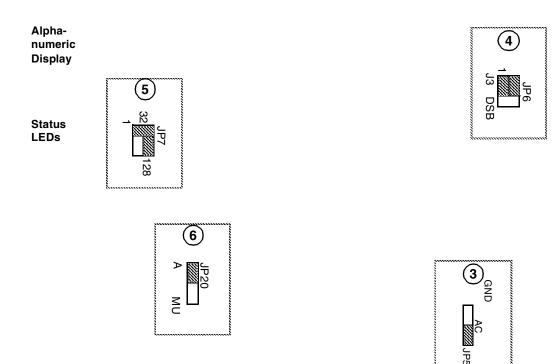

| 3.4 Status LEDs                      | 5  |

| 3.5 AAC Alarms                       | 7  |

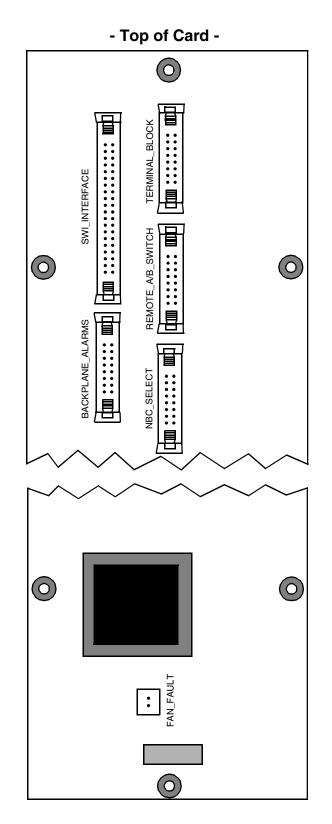

| 3.6 Connectors                       | 7  |

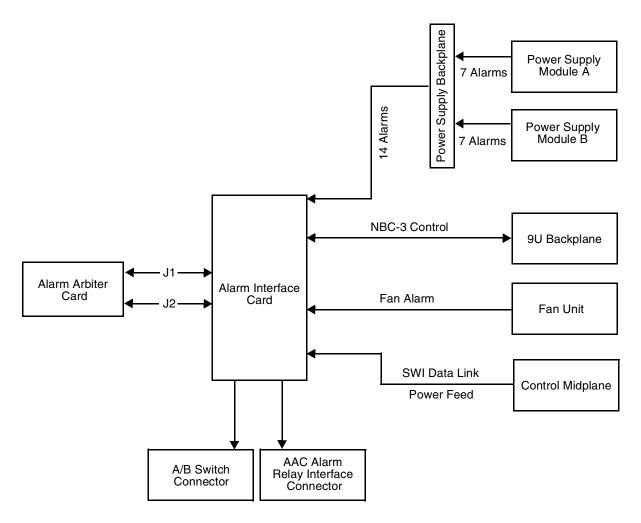

| 4.0 AIC CIRCUIT DESCRIPTION          | 9  |

| 5.0 CONFIGURATION NOTES              | 11 |

| 5.1 Alarm Arbiter Card               | 11 |

| 5.2 Alarm Interface Card             | 11 |

| 6.0 REMOVAL/REPLACEMENT INFORMATION  | 14 |

| 6.1 Alarm Arbiter Card               | 14 |

| 6.2 Alarm Interface Card             | 15 |

| 7.0 TROUBLESHOOTING                  | 15 |

| 8.0 RELATED DOCUMENTS                | 16 |

# Central Processing Unit (CPU - 16 MB)

| 1.0 GENERAL                                                | 1  |

|------------------------------------------------------------|----|

| 2.0 SPECIFICATIONS                                         | 1  |

| 3.0 CPU CARD CIRCUIT DESCRIPTION                           | 2  |

| 3.1 VMEbus Arbitration                                     | 2  |

| 3.2 On-Board dynamic Ram                                   | 3  |

| 3.3 Firmware                                               | 3  |

| 3.4 Real time clock                                        | 3  |

| 4.0 FUNCTIONAL DESCRIPTION OF THE CPU CARD                 | 3  |

| 4.1 Front Panel Switches and Indicators                    | 3  |

| 4.2 Connectors                                             | 5  |

| 5.0 CONFIGURATION NOTES                                    | 6  |

| 5.1 PROM Locations – CPU Card                              | 6  |

| 6.0 REMOVAL/REPLACEMENT INFORMATION                        | 8  |

| 6.1 Removing & Replacing System Controller Cards – General | 8  |

| 6.2 Removal Procedures                                     | 10 |

| 6.3 Replacement Procedures                                 | 11 |

| 7.0 TROUBLESHOOTING                                        | 12 |

| 7.1 Host Communications – System                           | 12 |

| 7.2 Fault Isolation - CPU Card                             | 12 |

| 8.0 RELATED DOCUMENTS                                      | 12 |

|                                                            |    |

## Combined Controller Assembly (CCA)

| 1.0 | GENERAL                                               | 1  |

|-----|-------------------------------------------------------|----|

| 2.0 | SPECIFICATIONS                                        | 3  |

| 3.0 | CPU CARD                                              | 4  |

|     | 3.1 Specifications                                    | 4  |

|     | 3.2 CPU Card Circuit Description                      | 4  |

|     | 3.3 Configuration Notes                               | 7  |

| 4.0 | SWITCH INTERFACE (SWI) AND FLOPPY DISK DRIVE ASSEMBLY | 8  |

|     | 4.1 Specifications                                    | 8  |

|     | 4.2 SWI Card Circuit Description                      | 9  |

|     | 4.3 Floppy Disk Drive Description                     | 11 |

|     | 4.4 Front Panel LEDs                                  | 11 |

| 5.0 | REMOVAL & REPLACEMENT PROCEDURES                      | 11 |

|     | 5.1 Combined Controller Assembly                      | 11 |

|     | 5.2 CPU Card                                          | 14 |

| 6.0 | TROUBLESHOOTING                                       | 15 |

|     | 6.1 Fault Isolation                                   | 15 |

|     | 6.2 Error Messages                                    | 16 |

|     | 6.3 LEDs                                              | 16 |

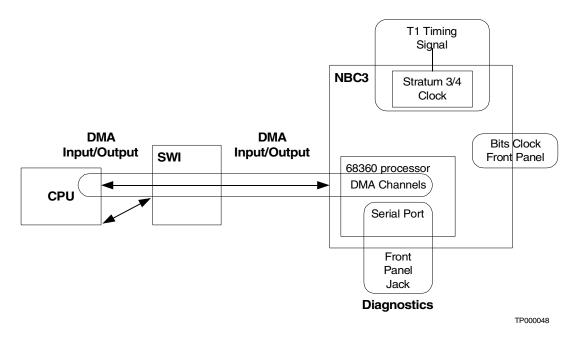

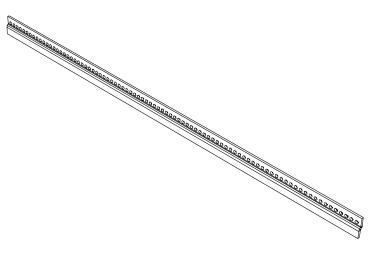

## Network Bus Controller 3 Card (NBC3)

| 1.0 GENERAL                                              | 1  |

|----------------------------------------------------------|----|

| 1.1 DTG-2 Mezzanine Card                                 | 1  |

| 2.0 SPECIFICATIONS                                       | 2  |

| 3.0 CIRCUIT DESCRIPTION                                  | 3  |

| 3.1 Communications Bus                                   | 3  |

| 3.2 Clock Synchronization                                | 3  |

| 3.3 SWI Interface                                        | 4  |

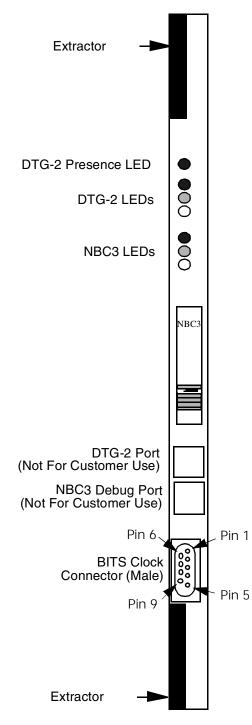

| 3.4 External Interfaces                                  | 5  |

| 3.5 NBC3 Status LEDs                                     | 7  |

| 3.6 Connector J1 Pin Assignments                         | 9  |

| 4.0 CONFIGURATION NOTES                                  | 10 |

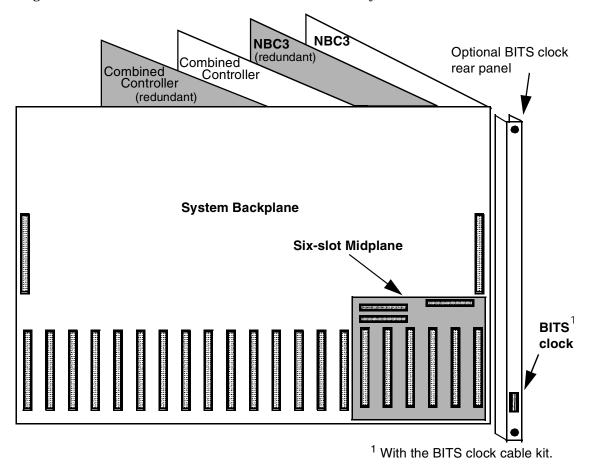

| 5.0 NBC3 CARD POPULATION RULES                           | 11 |

| 6.0 REMOVAL/REPLACEMENT PROCEDURES                       | 12 |

| 6.1 Removal Procedures                                   | 12 |

| 6.2 Replacement Procedures                               | 13 |

| 7.0 TROUBLESHOOTING                                      | 14 |

| 7.1 Troubleshooting Procedures For Non-redundant Systems | 14 |

| 7.2 Troubleshooting Procedures For Redundant Systems     | 14 |

| 8.0 RELATED DOCUMENTS                                    | 14 |

#### Direct Inward Dial Card (DID-2)

| 1.0 GENERAL                                 | 1  |

|---------------------------------------------|----|

| 2.0 SPECIFICATIONS                          | 1  |

| 2.1 Answer Supervision                      | 3  |

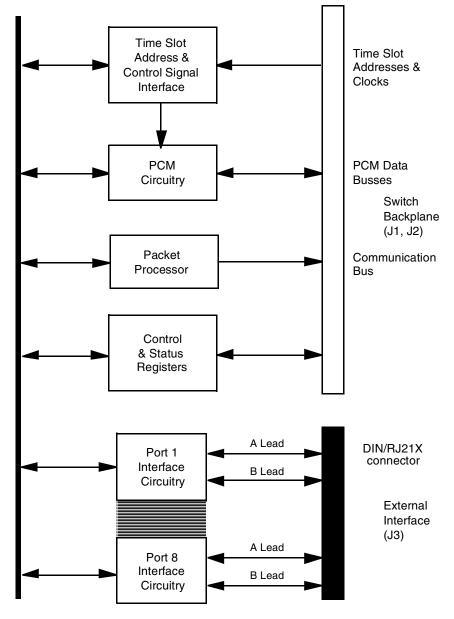

| 3.0 CIRCUIT DESCRIPTION                     | 3  |

| 3.1 Per Port Circuitry                      | 4  |

| 3.2 PCM Time Slot Bus Interface             | 7  |

| 3.3 Packet Processor                        | 7  |

| 3.4 PCM Bus Interfaces - J1 Pin Assignments | 7  |

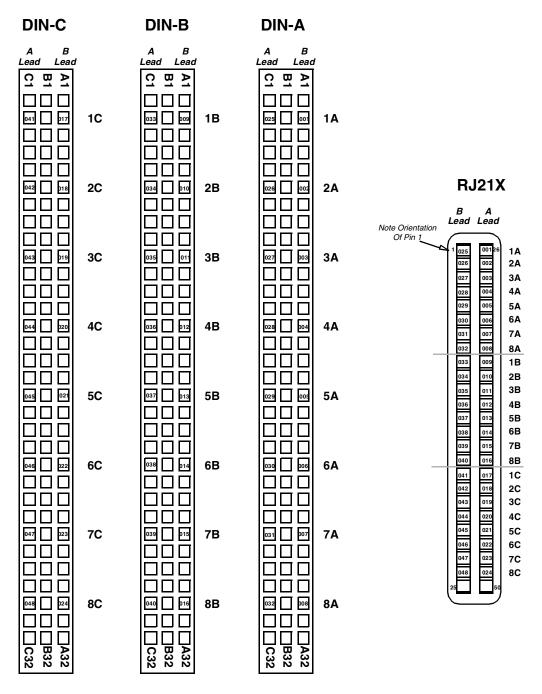

| 3.5 External Interfaces                     | 8  |

| 4.0 CONFIGURATION NOTES                     | 13 |

| 5.0 RELATED DOCUMENTS                       | 15 |

| 5.1 VCO Documentation                       | 15 |

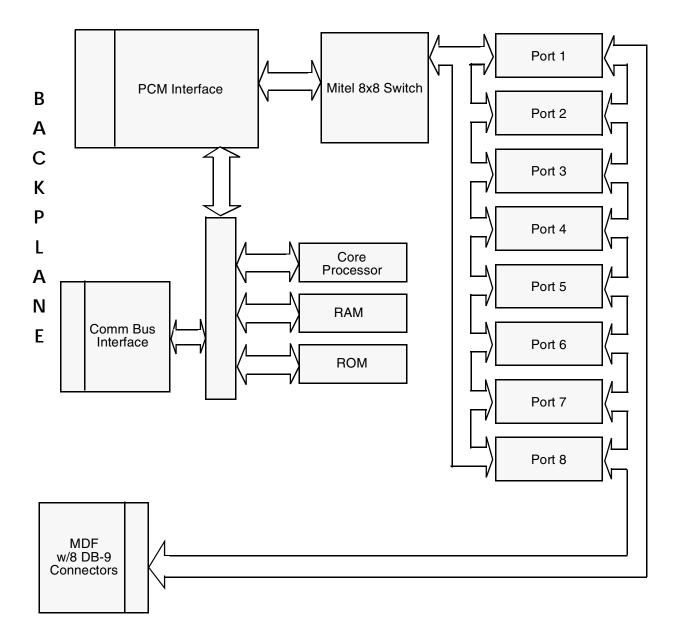

# Drop and Insert Card (D+I)

| 1.0 GENERAL             | 1 |

|-------------------------|---|

| 2.0 SPECIFICATIONS      | 1 |

| 3.0 CIRCUIT DESCRIPTION | 2 |

| 3.1 Mitel Switch       | 3 |

|------------------------|---|

| 3.2 Core Processor     | 3 |

| 3.3 PCM Bus            | 3 |

| 3.4 Comm Bus Interface | 3 |

| 3.5 Port Interface     | 4 |

## E+M Trunk Card (E+M)

| 1.0 | GENERAL                                     | 1  |

|-----|---------------------------------------------|----|

| 2.0 | SPECIFICATIONS                              | 1  |

| 3.0 | CIRCUIT DESCRIPTION                         | 2  |

|     | 3.1 Per Port Circuitry                      | 3  |

|     | 3.2 PCM Time Slot Bus Interface             | 7  |

|     | 3.3 Packet Processor                        | 7  |

|     | 3.4 PCM Bus Interfaces – J1 Pin Assignments | 7  |

|     | 3.5 External Interfaces                     | 10 |

| 4.0 | CONFIGURATION NOTES                         | 11 |

|     | 4.1 E+M Trunk Card                          | 13 |

| 5.0 | RELATED DOCUMENTS                           | 20 |

## Four Span Programmable T1 Interface Card (4xT1)

| 1.0 GENERAL                                       | 1  |

|---------------------------------------------------|----|

| 2.0 SPECIFICATIONS                                | 1  |

| 2.1 PROGRAMMABILITY                               | 1  |

| 3.0 CIRCUIT DESCRIPTION                           | 2  |

| 3.1 Shared Circuitry                              | 3  |

| 3.2 Individual Span Circuitry                     | 3  |

| 3.3 LED STATES                                    | 5  |

| 3.4 PIN ASSIGNMENTS                               | 5  |

| 4.0 CONFIGURATION NOTES                           | 8  |

| 4.1 MDF Adapter                                   | 8  |

| 4.2 Jumper Positions                              | 12 |

| 5.0 TROUBLESHOOTING                               | 13 |

| 5.1 Loss of synchronization of incoming reference | 13 |

| 5.2 Cards not coming into service                 | 13 |

## Interface Controller Card (ICC)

| 1.0 | GENERAL                       | 1 |

|-----|-------------------------------|---|

| 2.0 | SPECIFICATIONS                | 2 |

|     | 2.1 Compliance with Standards | 2 |

|     | 2.2 ICC Card Specifications   | 2 |

| 3.0 | ICC CARD ARCHITECTURE         | 2 |

| 4  |

|----|

| 7  |

| 8  |

| 8  |

| 9  |

| 9  |

| 9  |

| 9  |

| 10 |

| 10 |

|    |

#### Interface Controller Card T1 I/O Module

| 1.0 | GENERAL                       | 1 |

|-----|-------------------------------|---|

| 2.0 | SPECIFICATIONS                | 1 |

|     | 2.1 Compliance with Standards | 1 |

|     | 2.2 I/O Module Specifications | 2 |

| 3.0 | PROGRAMMABILITY               | 5 |

|     | 3.1 I/O Interface             | 5 |

| 4.0 | I/O MODULE DESCRIPTION        | 6 |

| 5.0 | CONFIGURATION NOTES           | 8 |

| 6.0 | RELATED DOCUMENTS             | 8 |

## Line Test Card-8 (LTC-8)

| 1.0 GENERAL                                  | 1  |

|----------------------------------------------|----|

| 2.0 PHYSICAL DESCRIPTION                     | 1  |

| 2.1 PCM Bus Interfaces – J1 Pin Assignments  | 3  |

| 2.2 External Interfaces - J3 PIN ASSIGNMENTS | 3  |

| 3.0 SPECIFICATIONS                           | 6  |

| 4.0 CIRCUIT DESCRIPTION                      | 7  |

| 4.1 Per Port Circuitry                       | 8  |

| 4.2 Packet Processor                         | 10 |

| 4.3 PCM timeslot Bus Interface               | 10 |

| 5.0 SOFTWARE CONFIGURATION                   | 11 |

| 6.0 RELATED DOCUMENTS                        | 11 |

# MVDC Programmable T1 Interface Card (MVDC)

| 1.0 GENERAL              | 1 |

|--------------------------|---|

| 2.0 SPECIFICATIONS       | 1 |

| 2.1 PROGRAMMABILITY      | 1 |

| 3.0 CIRCUIT DESCRIPTIION | 2 |

| 3.1 Shared Circuitr    | у                         | 3  |

|------------------------|---------------------------|----|

| 3.2 Individual Spar    | Circuitry                 | 3  |

| 3.3 Standards Com      | pliance                   | 4  |

| 3.4 LED STATES         |                           | 5  |

| 3.5 PIN ASSIGNM        | ENTS                      | 5  |

| 4.0 REMOVAL/REPLA      | CEMENT PROCEDURES         | 6  |

| Primary Rate Interface | /NFAS Card (PRI/N)        |    |

| 1.0 GENERAL            |                           | 1  |

| 2.0 SPECIFICATIONS     |                           | 2  |

| 3.0 CIRCUIT DESCRI     | PTION                     | 2  |

| 3.1 Overview Of Ci     | rcuit Operation           | 4  |

| 3.2 Physical Interfa   | ce                        | 4  |

| 3.3 IMP Processor      |                           | 5  |

| 3.4 PRI Framer         |                           | 9  |

| 3.5 Line Interface U   | Jnit                      | 9  |

| 3.6 PRI/N Card LE      | D States                  | 9  |

| 3.7 PCM Bus Inter      | aces - J1 Pin Assignments | 11 |

| 3.8 External Interf    | aces                      | 12 |

| 3.9 Line Equalizati    | on                        | 16 |

| 3.10 DIP Switch        |                           | 16 |

| 4.0 CONFIGURATION      | NOTES                     | 16 |

| 5.0 REMOVAL/REPLA      | CEMENT PROCEDURES         | 19 |

| 6.0 RELATED DOCUM      | IENTS                     | 19 |

# Subscriber Line Interface Card (SLIC-2)

| 1.0 | GENERAL                                     | 1  |

|-----|---------------------------------------------|----|

| 2.0 | SPECIFICATIONS                              | 1  |

| 3.0 | CIRCUIT DESCRIPTION                         | 2  |

|     | 3.1 Per Port Circuitry                      | 4  |

|     | 3.2 PCM Time Slot Bus Interface             | 6  |

|     | 3.3 Packet Processor                        | 6  |

|     | 3.4 PCM Bus Interfaces – J1 Pin Assignments | 6  |

|     | 3.5 External Interfaces                     | 7  |

| 4.0 | CONFIGURATION NOTES                         | 11 |

| 5.0 | RELATED DOCUMENTS                           | 13 |

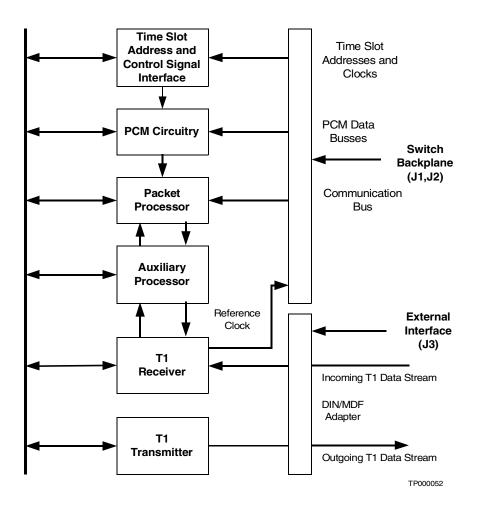

# T1 Interface Card (T1)

| 1.0 G  | ENERAL             | 1 |

|--------|--------------------|---|

| 2.0 SI | PECIFICATIONS      | 1 |

| 3.0 C  | IRCUIT DESCRIPTION | 2 |

|     | 3.1 Auxiliary Processor                     | 3  |

|-----|---------------------------------------------|----|

|     | 3.2 T1 Receiver                             | 4  |

|     | 3.3 T1 Transmitter                          | 4  |

|     | 3.4 Packet Processor                        | 5  |

|     | 3.5 T1 Card LED States                      | 5  |

|     | 3.6 PCM Bus Interfaces - J1 Pin Assignments | 7  |

|     | 3.7 External Interfaces                     | 7  |

|     | 3.8 T1 Line Equalization                    | 7  |

| 4.0 | CONFIGURATION NOTES                         | 11 |

| 5.0 | RELATED DOCUMENTATION                       | 13 |

# Universal Trunk Card (UTC-2)

| 1.0 | GENERAL                                   | 1  |

|-----|-------------------------------------------|----|

| 2.0 | SPECIFICATIONS                            | 1  |

| 3.0 | CIRCUIT DESCRIPTION                       | 3  |

|     | 3.1 Per Port Circuitry                    | 4  |

|     | 3.2 DTMF Digit Receiver                   | 4  |

|     | 3.3 Analog to Digital Encoding & Decoding | 4  |

|     | 3.4 Analog Interface                      | 5  |

|     | 3.5 On/Off Hook & Ground Start Relays     | 5  |

|     | 3.6 Ring Voltage & Current Flow Detectors | 5  |

|     | 3.7 Tip & Ring Protective Devices         | 6  |

| 4.0 | PCM TIME SLOT BUS INTERFACE               | 6  |

| 5.0 | PACKET PROCESSOR                          | 7  |

| 6.0 | PCM BUS INTERFACES - J1 PIN ASSIGNMENTS   | 7  |

| 7.0 | EXTERNAL INTERFACES                       | 7  |

| 8.0 | CONFIGURATION NOTES                       | 13 |

| 9.0 | RELATED DOCUMENTS                         | 17 |

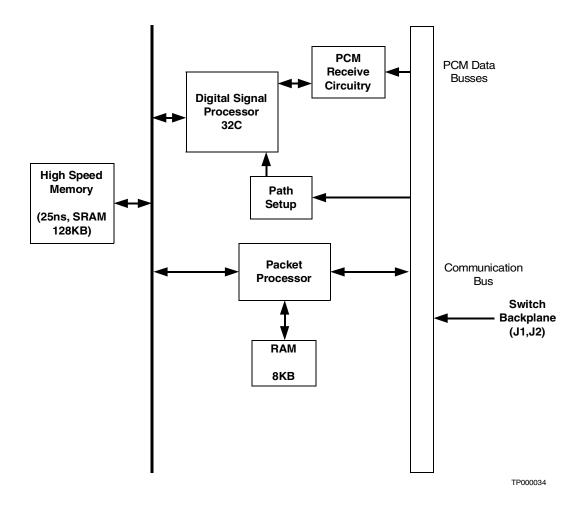

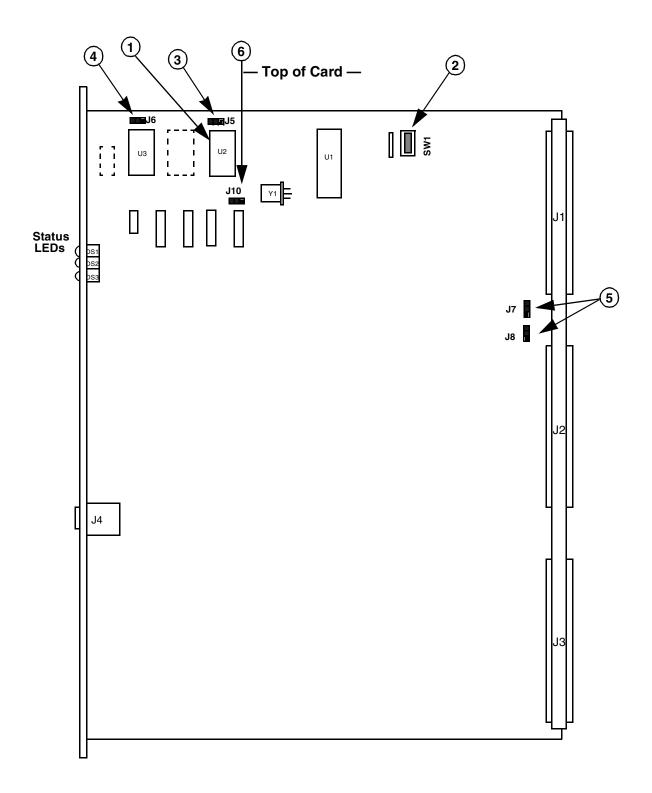

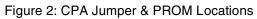

# Call Progress Analyzer Card (CPA)

| 1.0 | GENERAL                                 | 1 |

|-----|-----------------------------------------|---|

| 2.0 | SPECIFICATIONS                          | 1 |

| 3.0 | CIRCUIT DESCRIPTION                     | 2 |

|     | 3.1 Digital Signal Processor            | 2 |

|     | 3.2 Packet Processor                    | 4 |

|     | 3.3 Communication Bus Interface         | 4 |

|     | 3.4 PCM Receive Circuitry               | 5 |

|     | 3.5 CPA Status LEDs                     | 5 |

|     | 3.6 Backplane Connector Pin Assignments | 5 |

| 4.0 | CONFIGURATION NOTES                     | 5 |

| 5.0 | REMOVAL/REPLACEMENT PROCEDURES          | 9 |

| 6.0 TROUBLESHOOTING                 | 10 |

|-------------------------------------|----|

| 6.1 Failure To Download             | 10 |

| 6.2 Loss Of CPA — Effect On Service | 10 |

| 7.0 RELATED DOCUMENTS               | 10 |

| 7.1 VCO/4K systems                  | 10 |

#### **Digital Conference Card (DCC)**

| 1.0 | GENERAL                                     | 1 |

|-----|---------------------------------------------|---|

| 2.0 | SPECIFICATIONS                              | 1 |

| 3.0 | DESCRIPTION                                 | 1 |

|     | 3.1 Conferencing Logic                      | 2 |

|     | 3.2 PCM Transmit Circuitry                  | 3 |

|     | 3.3 Packet Processor                        | 3 |

|     | 3.4 DCC Status LEDs                         | 4 |

|     | 3.5 PCM Bus Interfaces - J1 Pin Assignments | 4 |

| 4.0 | CONFIGURATION NOTES                         | 6 |

| 5.0 | TROUBLESHOOTING                             | 8 |

|     | 5.1 Loss Of DCC—Effect on Service           | 8 |

| 6.0 | RELATED DOCUMENTS                           | 8 |

# Digital Tone Generator Card (DTG)

| 1.0 GENERAL                                 | 1  |

|---------------------------------------------|----|

| 2.0 SPECIFICATIONS                          | 1  |

| 3.0 CIRCUIT DESCRIPTION                     | 4  |

| 3.1 Tone Generator Operation                | 5  |

| 3.2 Packet Processor                        | 6  |

| 3.3 PCM Bus Interfaces - J1 Pin Assignments | 6  |

| 4.0 CONFIGURATION NOTES                     | 8  |

| 5.0 TROUBLESHOOTING                         | 10 |

| 5.1 Resetting A DTG Card                    | 10 |

| 6.0 RELATED DOCUMENTS                       | 10 |

## Digital Tone Generator 2 Card (DTG-2)

| 1.0 | GENERAL                      | 1 |

|-----|------------------------------|---|

| 2.0 | SPECIFICATIONS               | 1 |

| 3.0 | CIRCUIT DESCRIPTION          | 1 |

|     | 3.1 Tone Generator Operation | 2 |

|     | 3.2 Packet Processor         | 5 |

|     | 3.3 Redundancy               | 5 |

|     | 3.4 DTG-2 Status LEDs        | 6 |

| 4.0 | CONFIGURATION NOTES          | 7 |

| 5.0 DTG-2 REMOVAL AND REPLACEMENT PROCEDURES                  | 8       |

|---------------------------------------------------------------|---------|

| 5.1 Removing a DTG-2 Card                                     | 8       |

| 5.2 Replacing a DTG-2 Card                                    | 9       |

| 6.0 TROUBLESHOOTING                                           | 9       |

| 6.1 Detecting and Correcting DTG-2 Problems                   | 9       |

| 6.2 Resetting A DTG-2 Card On Redundant Systems               | 10      |

| 7.0 RELATED DOCUMENTS                                         | 10      |

| DTMF Receiver Card (DRC-8)                                    |         |

| 1.0 GENERAL                                                   | 1       |

| 2.0 SPECIFICATIONS                                            | 1       |

| 3.0 CIRCUIT DESCRIPTION                                       | 2       |

| 3.1 DTMF Digit Receiver                                       | 3       |

| 3.2 PCM Time Slot Bus Interface                               | 3       |

| 3.3 Packet Processor                                          | 3       |

| 3.4 DRC Status LEDs                                           | 4       |

| 3.5 PCM Bus Interfaces - J1 Pin Assignments                   | 4       |

| 4.0 CONFIGURATION NOTES                                       | 5       |

| 5.0 RELATED DOCUMENTS                                         | 7       |

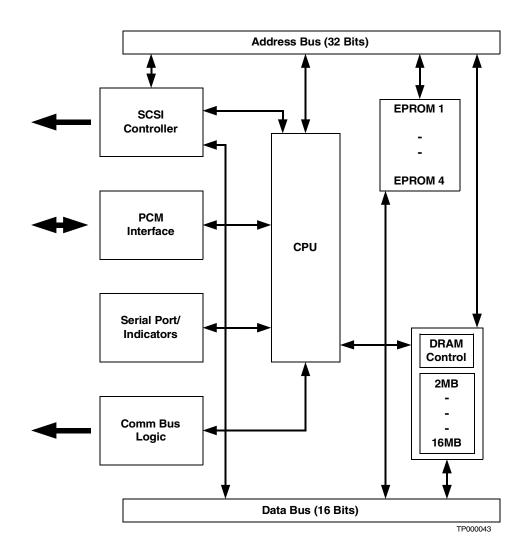

| INTEGRATED PROMPT/RECORD CARD (IPRC)                          |         |

| 1.0 GENERAL                                                   | 1       |

| 2.0 SPECIFICATIONS                                            | 1       |

| 3.0 CIRCUIT DESCRIPTION                                       | 2       |

| 3.1 DRAM Prompt Storage                                       | 2       |

| 3.2 PCM Time Slot Bus Interface                               | 2       |

| 3.3 Packet Processor                                          | 4       |

| 3.4 IPRC Status LEDs                                          | 4       |

| 3.5 SCSI Interface                                            | 5       |

| 4.0 EXTERNAL INTERFACES                                       | 6       |

| 4.1 J1 Pin Assignments                                        | 6       |

| 4.2 J3 Pin Assignments                                        | 7       |

| 4.3 Front Panel Jack (P2)                                     | 9       |

| 5.0 CONFIGURATION NOTES                                       | 9<br>9  |

| 5.1 EPROM Select Jumpers<br>5.2 Reset Jumper                  | 9<br>10 |

| 5.2 Keset Jumper<br>5.3 Software Configurable Port Limitation | 10      |

| sie bottmate comparation of Limitation                        | 10      |

6.0 RELATED DOCUMENTS

10

## MF Receiver Card (MRC)

| 1.0 GENERAL                                 | 1 |

|---------------------------------------------|---|

| 2.0 SPECIFICATIONS                          | 1 |

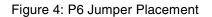

| 3.0 CIRCUIT DESCRIPTION                     | 2 |

| 3.1 MF Digit Receiver                       | 2 |

| 3.2 PCM Time Slot Bus Interface             | 3 |

| 3.3 Packet Processor                        | 3 |

| 3.4 Control Status Registers                | 3 |

| 3.5 MRC Status LEDs                         | 4 |

| 3.6 PCM Bus Interfaces - J1 Pin Assignments | 4 |

| 4.0 CONFIGURATION NOTES                     | 5 |

| 5.0 RELATED DOCUMENTS                       | 7 |

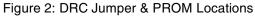

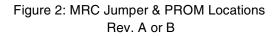

# DTMF Receiver Cards (DRC-24 and DRC-48)

| 1.0 GENERAL                                     | 1  |

|-------------------------------------------------|----|

| 2.0 SPECIFICATIONS                              | 1  |

| 3.0 CIRCUIT DESCRIPTION                         | 2  |

| 3.1 Digital Signal Processor                    | 3  |

| 3.2 Packet Processor                            | 3  |

| 3.3 Communication Bus Interface                 | 3  |

| 3.4 PCM Receive Circuitry                       | 3  |

| 3.5 DRC-24 and DRC-48 Status LEDs               | 4  |

| 3.6 Backplane Connector Pin Assignments         | 5  |

| 4.0 CONFIGURATION NOTES                         | 5  |

| 5.0 TROUBLESHOOTING                             | 9  |

| 5.1 Failure To Download                         | 9  |

| 5.2 Loss Of DRC-24 or DRC-48: Effect On Service | 10 |

| 6.0 RELATED DOCUMENTS                           | 10 |

#### Subrate Switching Card (SSC)

| 1.0 | GENERAL DESCRIPTION        | 1 |

|-----|----------------------------|---|

| 2.0 | SPECIFICATIONS             | 1 |

| 3.0 | REDUNDANCY                 | 1 |

| 4.0 | CIRCUIT DESCRIPTION        | 2 |

|     | 4.1 Circuitry              | 2 |

| 5.0 | CONFIGURATION NOTES        | 2 |

|     | 5.1 Hardware Configuration | 2 |

|     | 5.2 Software Configuration | 2 |

# Service Platform Card (SPC)

| 1.0 GENERAL                                | 1  |

|--------------------------------------------|----|

| 2.0 SPECIFICATIONS                         | 2  |

| 2.1 Compliance with Standards              | 2  |

| 2.2 SPC Card Specifications                | 2  |

| 3.0 SPC CARD ARCHITECTURE                  | 2  |

| 4.0 CORE PROCESSOR                         | 4  |

| 4.1 Core Processor Implementation          | 5  |

| 4.2 HDLC-based multiprocessor Architecture | 5  |

| 4.3 Command / Response data Routing        | 6  |

| 4.4 Alpha Display/Power Failure LED        | 7  |

| 5.0 COMMUNICATIONS BUS INTERFACE           | 7  |

| 6.0 SERVICE RESOURCE MODULES               | 8  |

| 6.1 DSP-Based Service Engine               | 8  |

| 6.2 Mezzanine Interface Architecture       | 8  |

| 6.3 Serial Mezzanine Boot Control          | 8  |

| 7.0 PROGRAMMABILITY                        | 9  |

| 8.0 MEMORY SUBSYSTEM                       | 9  |

| 8.1 Memory Controller                      | 9  |

| 8.2 DRAM                                   | 9  |

| 8.3 FLASH Memory                           | 10 |

| 9.0 PCM INTERFACE                          | 10 |

| 9.1 Bus Support                            | 10 |

| 10.0 POWER SUBSYSTEM                       | 10 |

| 11.0 CONFIGURATION NOTES                   | 10 |

| 12.0 REMOVAL/REPLACEMENT PROCEDURES        | 11 |

| 12.1 Removing an SRM Module                | 11 |

| 12.2 Adding an SRM Module                  | 11 |

| 13.0 RELATED DOCUMENTS                     | 12 |

| Direct Dial Inward Card (DDI)              |    |

| 1.0 GENERAL                                | 1  |

| 2.0 SPECIFICATIONS                         | 1  |

| 3.0 CIRCUIT DESCRIPTION                    | 3  |

| 3.1 Per Port Circuitry                     | 4  |

|     | 5.1 Fei Foit Circuitiy                      | 4  |

|-----|---------------------------------------------|----|

|     | 3.2 PCM Time Slot Bus Interface             | 5  |

|     | 3.3 Packet Processor                        | 6  |

|     | 3.4 PCM Bus Interfaces — J1 Pin Assignments | 6  |

|     | 3.5 External Interfaces                     | 6  |

| 4.0 | 0 CONFIGURATION NOTES                       | 11 |

|     | 4.1 Direct Dial Inward Card                 | 13 |

#### E1-Channel Associated Signalling Card (E1-CAS)

| 1.0 | GENERAL                                     | 1  |

|-----|---------------------------------------------|----|

| 2.0 | SPECIFICATIONS                              | 1  |

| 3.0 | CIRCUIT DESCRIPTION                         | 2  |

|     | 3.1 Overview of Circuit Operation           | 3  |

| 4.0 | PHYSICAL INTERFACE                          | 3  |

|     | 4.1 Packet Processor                        | 4  |

|     | 4.2 CEPT Framer                             | 4  |

|     | 4.3 Line Interface Unit                     | 6  |

|     | 4.4 E1 LED States                           | 7  |

|     | 4.5 PCM Bus Interfaces – J1 Pin Assignments | 9  |

| 5.0 | EXTERNAL INTERFACES                         | 10 |

| 6.0 | CONFIGURATION NOTES                         | 13 |

|     | 6.1 DIP Switch                              | 14 |

| 7.0 | RELATED DOCUMENTS                           | 14 |

# Earth/Loop Connect Trunk Card (ECT/LCT)

| 1.0 | GENERAL                                     | 1  |

|-----|---------------------------------------------|----|

| 2.0 | SPECIFICATIONS                              | 1  |

| 3.0 | CIRCUIT DESCRIPTION                         | 2  |

|     | 3.1 Per Port Circuitry                      | 4  |

|     | 3.2 DTMF Digit Receiver                     | 4  |

|     | 3.3 Analog Interface                        | 4  |

|     | 3.4 On/Off Hook & Earth Start Relays        | 4  |

|     | 3.5 Ring Voltage and Current Flow Detectors | 5  |

|     | 3.6 PCM Time Slot Bus Interface             | 5  |

|     | 3.7 Packet Processor                        | 5  |

|     | 3.8 PCM Bus Interfaces - J1 Pin Assignments | 6  |

|     | 3.9 External Interfaces                     | 6  |

| 4.0 | CONFIGURATION NOTES                         | 11 |

|     | 4.1 Earth Calling                           | 13 |

|     | 4.2 Loop Calling                            | 13 |

| 5.0 | RELATED DOCUMENTS                           | 14 |

|     |                                             |    |

# International E+M Trunk Card (E+M/DC5)

| 1.0 GENERAL        | 1 |

|--------------------|---|

| 2.0 SPECIFICATIONS | 1 |

| 3.0 CIRCUIT DESCRIPTION         | 3  |

|---------------------------------|----|

| 3.1 Per Port Circuitry          | 4  |

| 3.2 PCM Time Slot Bus Interface | 6  |

| 3.3 Packet Processor            | 7  |

| 3.4 External Interfaces         | 8  |

| 4.0 CONFIGURATION NOTES         | 11 |

| 5.0 RELATED DOCUMENTS           | 15 |

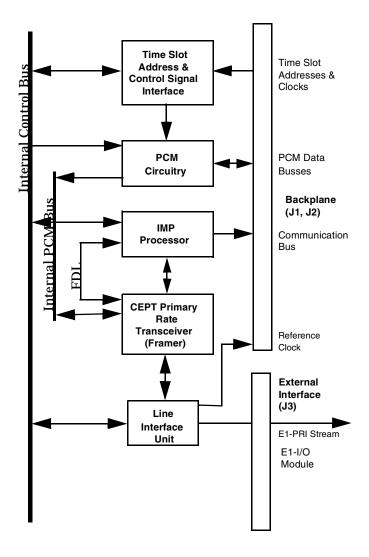

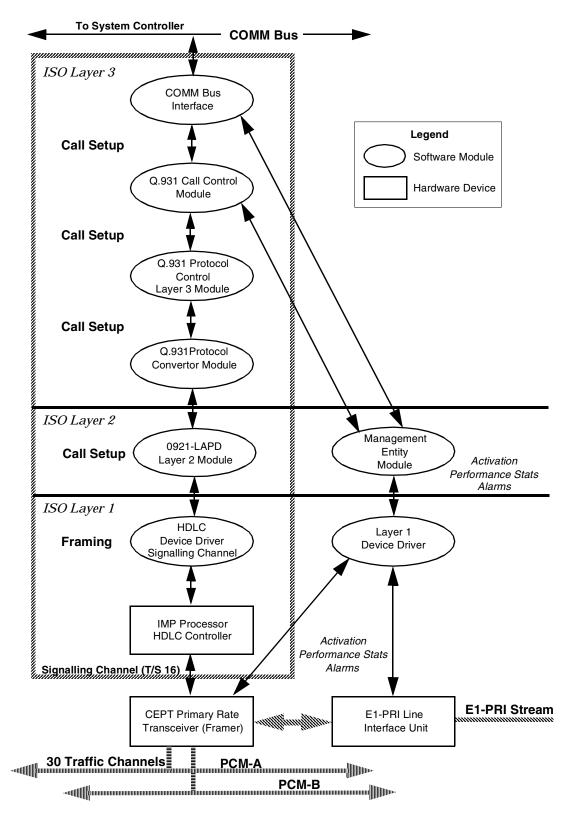

## E1-Primary Rate Interface Card (E1-PRI)

| 1.0 | GENERAL                                     | 1  |

|-----|---------------------------------------------|----|

| 2.0 | SPECIFICATIONS                              | 2  |

| 3.0 | CIRCUIT DESCRIPTION                         | 2  |

|     | 3.1 Overview of Circuit Operation           | 3  |

|     | 3.2 Physical Interface                      | 4  |

|     | 3.3 IMP Processor                           | 4  |

|     | 3.4 CEPT Primary Rate Transceiver (Framer)  | 8  |

|     | 3.5 Line Interface Unit                     | 8  |

|     | 3.6 E1-PRI Card LED States                  | 8  |

|     | 3.7 PCM Bus Interfaces - J1 Pin Assignments | 9  |

|     | 3.8 External Interfaces                     | 9  |

|     | 3.9 DIP Switch                              | 9  |

| 4.0 | CONFIGURATION NOTES                         | 15 |

| 5.0 | RELATED DOCUMENTS                           | 17 |

# Four Span Programmable E1 Interface Card (4xE1)

| 1.0 GENERAL                   | 1  |

|-------------------------------|----|

| 1.1 Timing                    | 1  |

| 2.0 SPECIFICATIONS            | 2  |

| 3.0 PROGRAMMABILITY           | 2  |

| 4.0 CIRCUIT DESCRIPTION       | 2  |

| 4.1 Shared Circuitry          | 3  |

| 4.2 Individual Span Circuitry | 4  |

| 5.0 LED STATES                | 5  |

| 6.0 PIN ASSIGNMENTS           | 6  |

| 7.0 CONFIGURATION NOTES       | 8  |

| 7.1 Plug-In Adapter           | 8  |

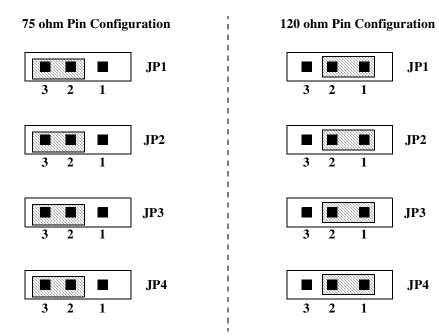

| 7.2 Jumper Positions          | 12 |

#### Interface Controller Card E1 I/O Module

| 1.0     | GENERAL                           | 1  |

|---------|-----------------------------------|----|

| 2.0     | SPECIFICATIONS                    | 2  |

|         | 2.1 Compliance with Standards     | 2  |

|         | 2.2 I/O Module Specifications     | 2  |

| 3.0     | PROGRAMMABILITY                   | 5  |

|         | 3.1 I/O Interface                 | 5  |

| 4.0     | I/O MODULE DESCRIPTION            | 6  |

| 5.0     | CONFIGURATION NOTES               | 8  |

| 6.0     | RELATED DOCUMENTS                 | 8  |

| Interfa | ace Controller Card J1 I/O Module |    |

| 1.0     | GENERAL                           | 9  |

| 2.0     | SPECIFICATIONS                    | 10 |

|         | 2.1 Compliance with Standards     | 10 |

|         | 2.2 I/O Module Specifications     | 10 |

| 3.0     | PROGRAMMABILITY                   | 13 |

|         | 3.1 I/O Interface                 | 13 |

| 4.0     | I/O MODULE DESCRIPTION            | 14 |

| 5.0     | CONFIGURATION NOTES               | 16 |

| 6.0 RELATED DOCUMENTS |  |

|-----------------------|--|

|-----------------------|--|

16

#### Multifrequency R2 Transceiver Card (MFC-R2)

| 1.0 | GENERAL                                     | 1  |

|-----|---------------------------------------------|----|

| 2.0 | SPECIFICATIONS                              | 1  |

| 3.0 | CIRCUIT DESCRIPTION                         | 6  |

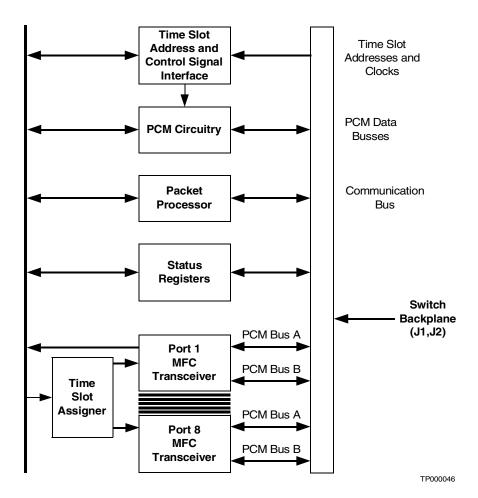

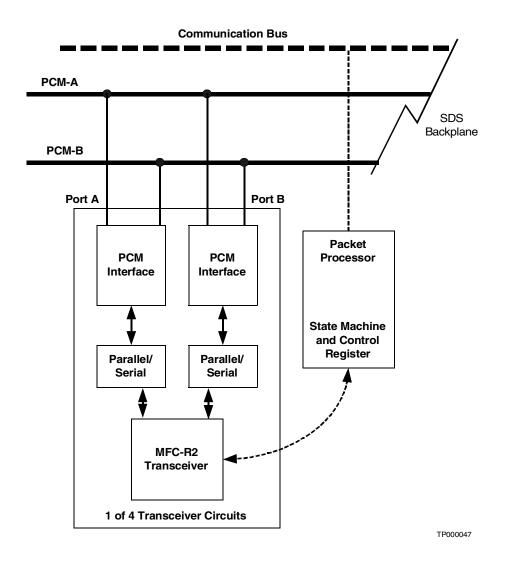

|     | 3.1 MFC Transceivers                        | 7  |

|     | 3.2 PCM Time Slot Bus Interface             | 9  |

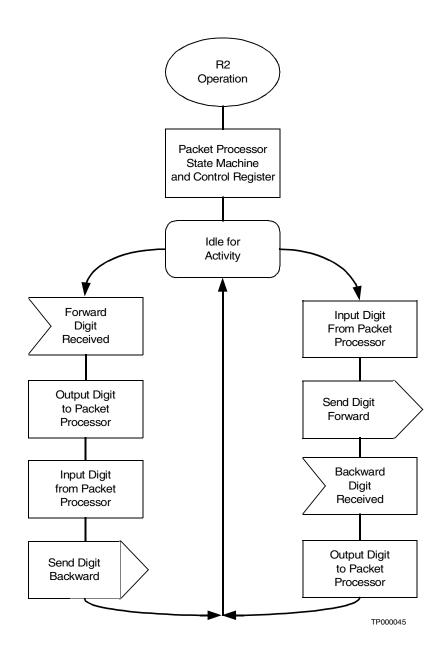

|     | 3.3 Packet Processor                        | 9  |

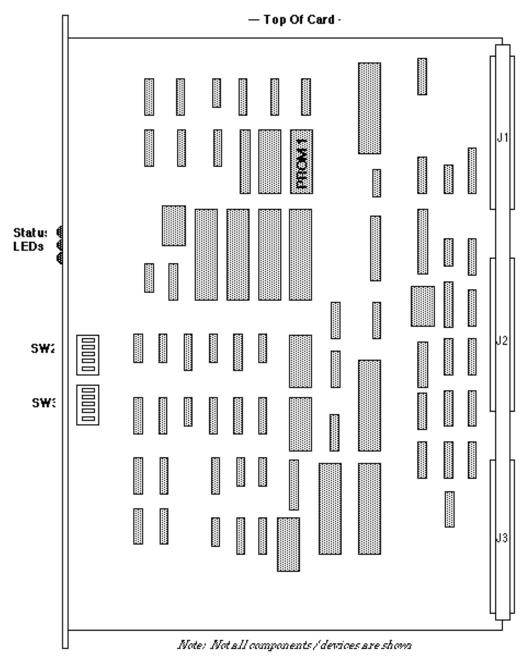

|     | 3.4 MFC-R2 Status LEDs                      | 9  |

|     | 3.5 Gain Control and Companding Types       | 10 |

|     | 3.6 PCM Bus Interfaces - J1 Pin Assignments | 10 |

|     | 3.7 PCM Bus Interfaces - J3 Pin Assignments | 10 |

| 4.0 | CONFIGURATION NOTES                         | 12 |

| 5.0 | RELATED DOCUMENTS                           | 14 |

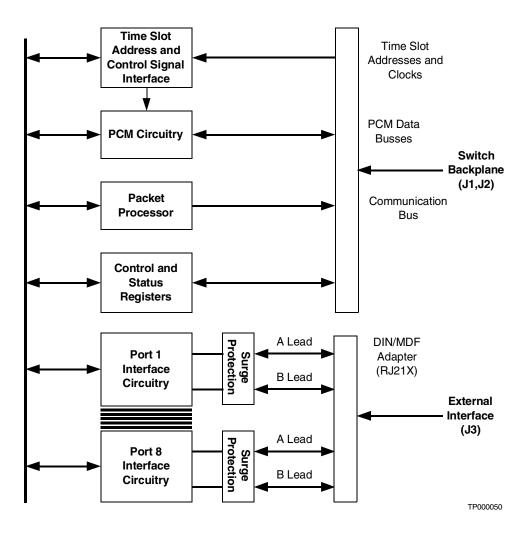

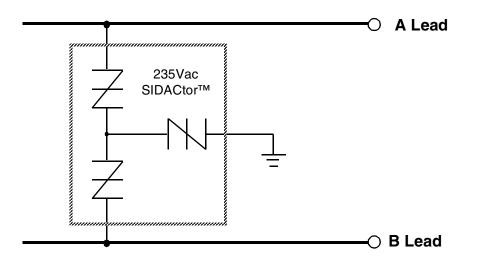

# Subscriber Line Interface Card for International (SLIC-INT)

| 1.0 GEN | NERAL        | 1 |

|---------|--------------|---|

| 2.0 SPE | ECIFICATIONS | 1 |

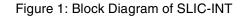

| 3.0 CIRCUIT DESCRIPTION                                       | 2  |

|---------------------------------------------------------------|----|

| 3.1 Per Port Circuitry                                        | 3  |

| 3.2 PCM Time Slot Bus Interface                               | 6  |

| 3.3 Packet Processor                                          | 6  |

| 3.4 PCM Bus Interfaces – J1 Pin Assignments                   | 6  |

| 3.5 External Interfaces                                       | 7  |

| 4.0 CONFIGURATION NOTES                                       | 12 |

| 4.1 Subscriber Line Interface Card - International (SLIC-INT) | 14 |

| 5.0 RELATED DOCUMENTS                                         | 14 |

## T1-E Interface Card (T1-E)

| 1.0 GENERAL                                           | 1      |

|-------------------------------------------------------|--------|

| 2.0 SPECIFICATIONS                                    | 1      |

| 3.0 CIRCUIT DESCRIPTION                               | 2      |

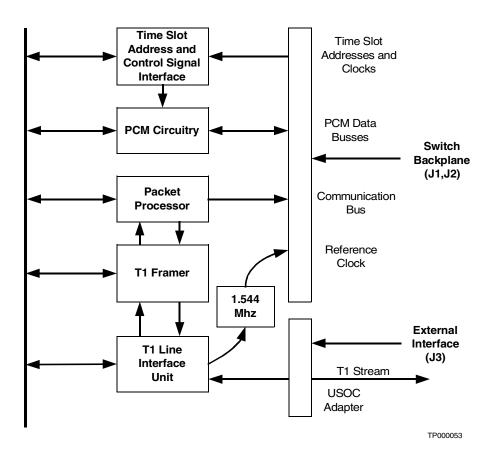

| 3.1 Overview of Circuit Operation                     | 3      |

| 3.2 Physical Interface                                | 3      |

| 3.3 Auxiliary Processor                               | 4      |

| 3.4 Packet Processor                                  | 4      |

| 3.5 T1-E Framer                                       | 4      |

| 3.6 Line Interface Unit                               | 5      |

| 3.7 T1-E Card LED States                              | 5      |

| 3.8 PCM Bus Interfaces - J1 Pin Assignments           | 6      |

| 3.9 External Interfaces                               | 7      |

| 3.10 Line Equalization                                | 10     |

| 3.11 DIP Switch Settings                              | 10     |

| 4.0 CONFIGURATION NOTES                               | 11     |

| 5.0 RELATED DOCUMENTS                                 | 14     |

| 6.0 DIP SWITCH SETTINGS FOR FIRMWARE, VERSION 9 (JAPA | AN) 14 |

#### VCO/4K Card Overview

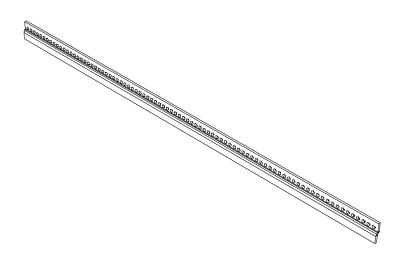

| Figure 1.1: PCB Card Retainer Bar   | 2 |

|-------------------------------------|---|

| Figure 1.2: Analog Card Front Panel | 4 |

#### Alarm Arbiter Card (AAC)with Alarm Interface Card (AIC)

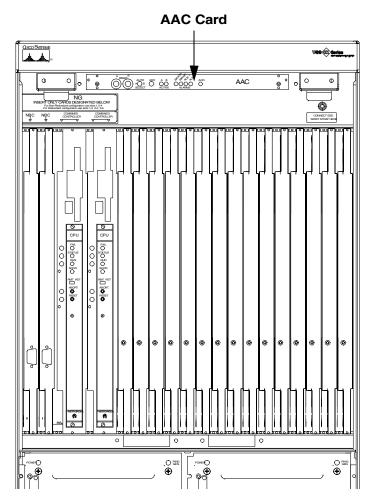

| Figure 1: | AAC Location                          | 1  |

|-----------|---------------------------------------|----|

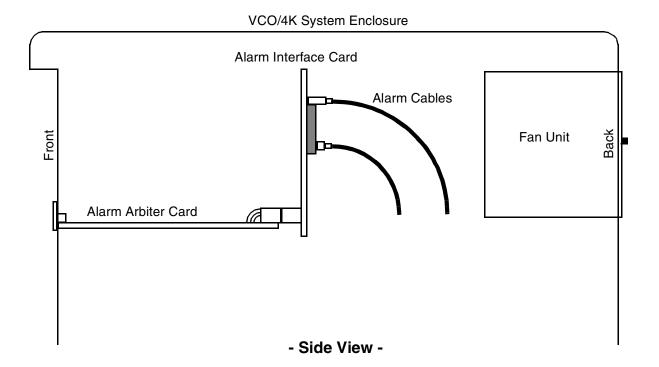

| Figure 2: | Location of the AAC and AIC           | 2  |

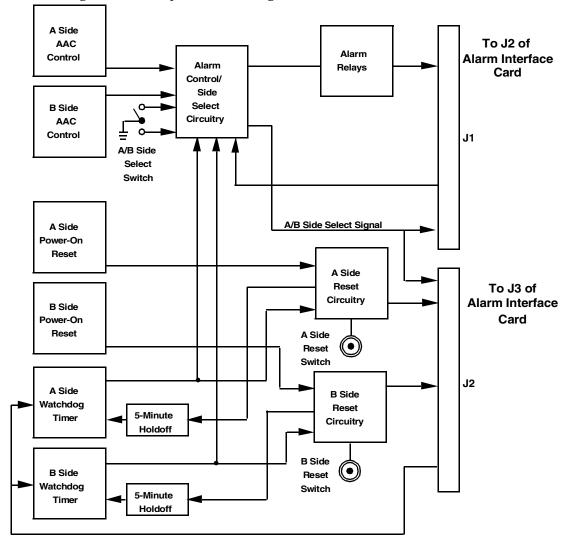

| Figure 3: | Block Diagram of Alarm Arbiter Card   | 3  |

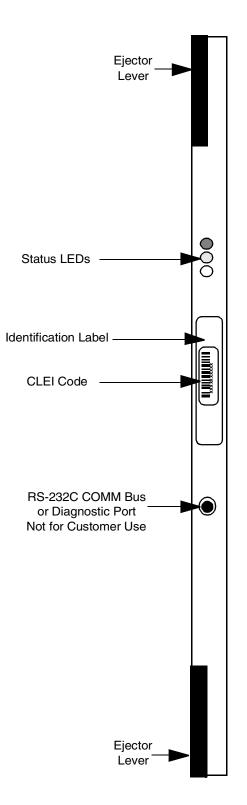

| Figure 4: | AAC Front Panel                       | 6  |

| Figure 5: | Block Diagram of Alarm Interface Card | 10 |

| Figure 6: | AAC Jumper Locations                  | 12 |

| Figure 7: | AIC Cable Connectors                  | 13 |

#### Central Processing Unit (CPU - 16 MB)

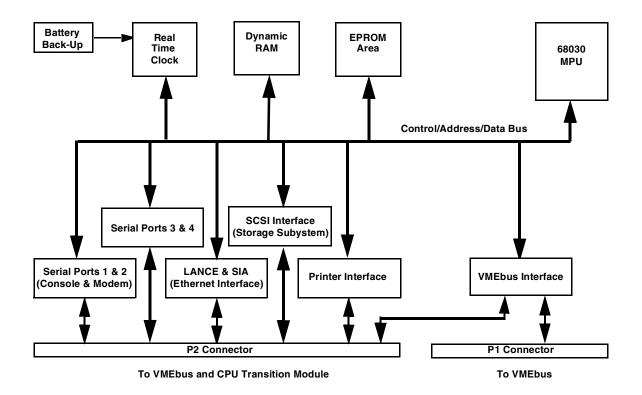

| Figure 1: Block Diagram of the CPU Card      | 2 |

|----------------------------------------------|---|

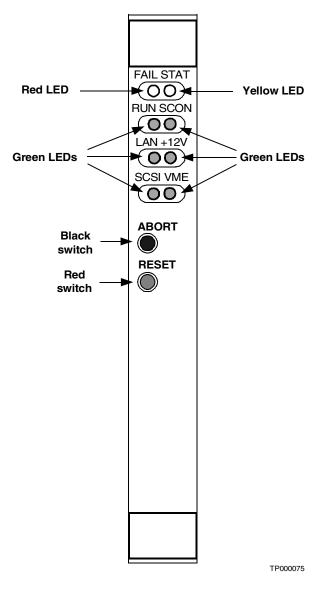

| Figure 2: CPU Card Front Panel               | 4 |

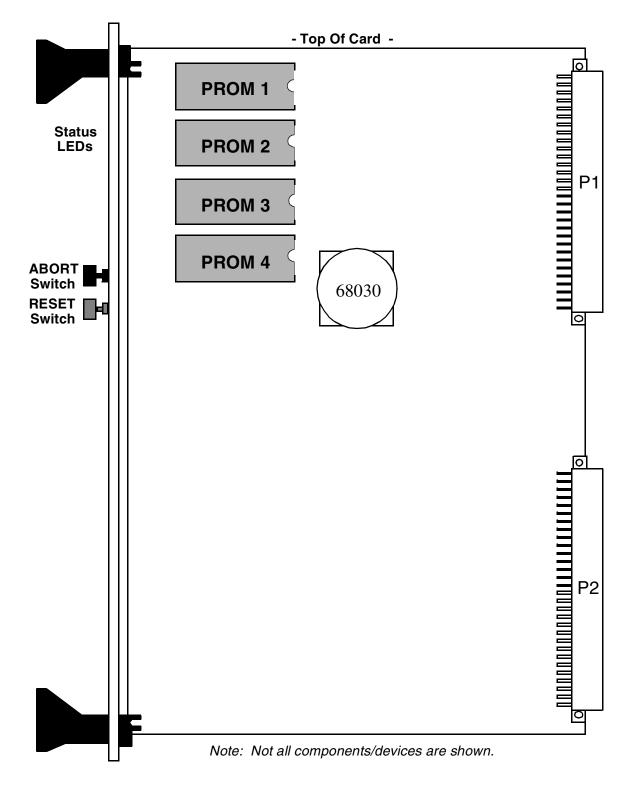

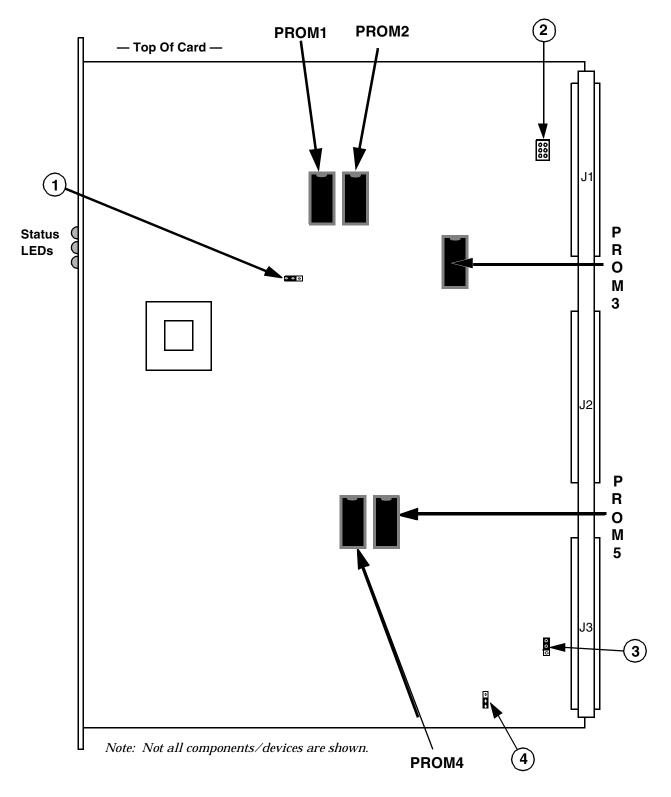

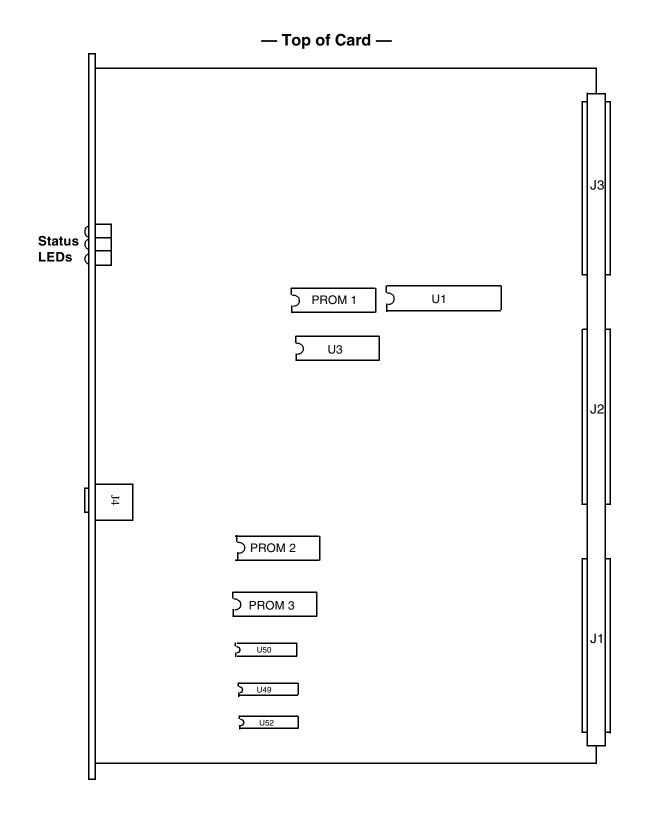

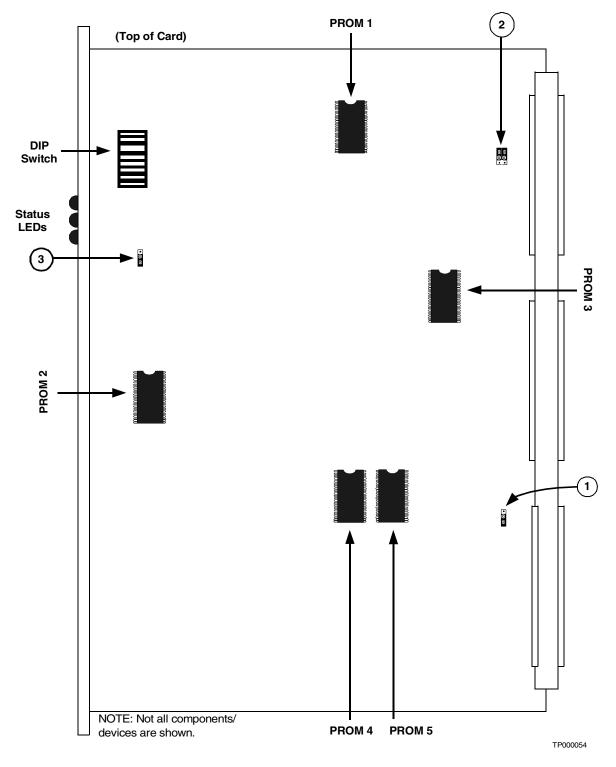

| Figure 3: CPU Card Jumper and PROM Locations | 7 |

| Figure 4: PCB Card Retainer Bar              | 9 |

#### **Combined Controller Assembly (CCA)**

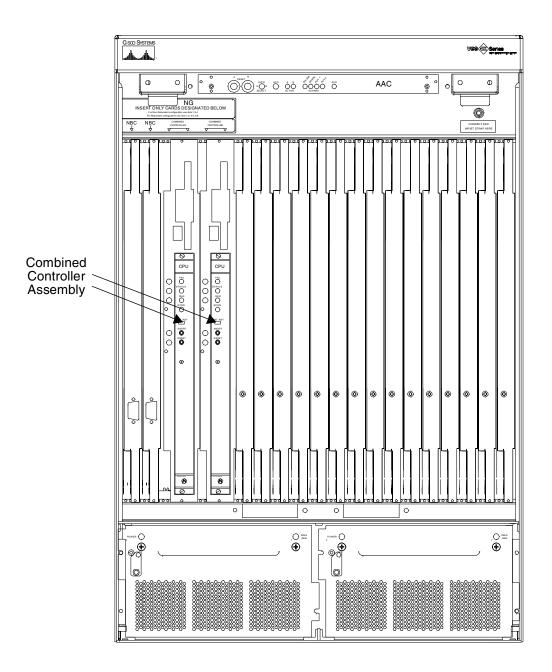

| Figure 1: Combined Controller Assembly (Front Panel) | 2  |

|------------------------------------------------------|----|

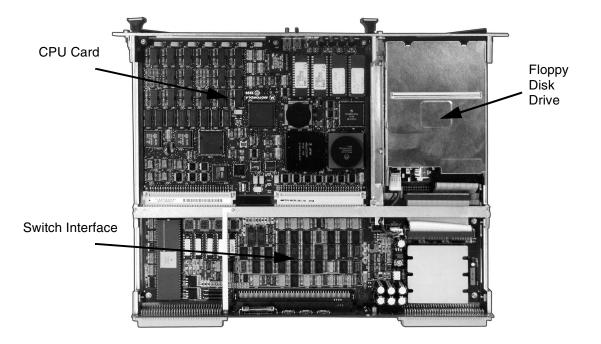

| Figure 2: Combined Controller Assembly (Top View)    | 3  |

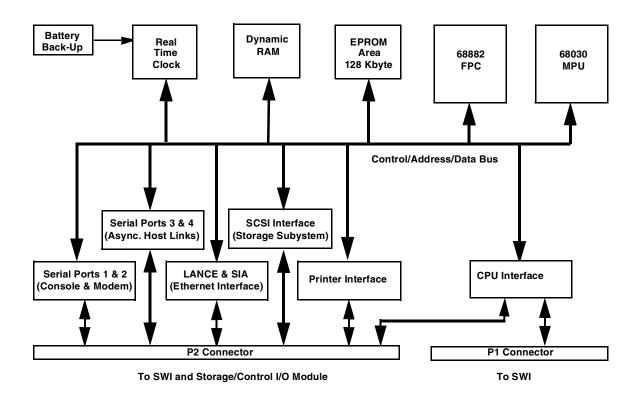

| Figure 3: Block Diagram of CPU Card                  | 5  |

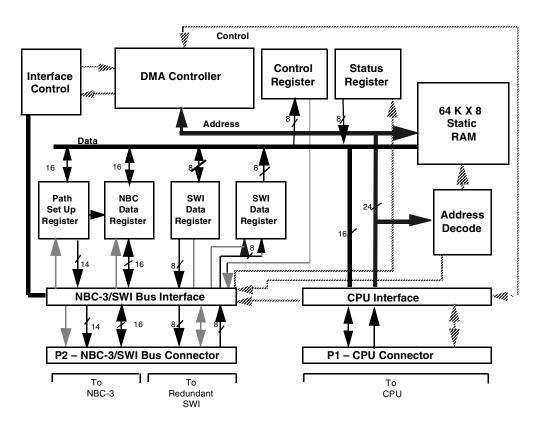

| Figure 4: Block Diagram of SWI Card                  | 10 |

| Figure 5: PCB Card Retainer Bar                      | 12 |

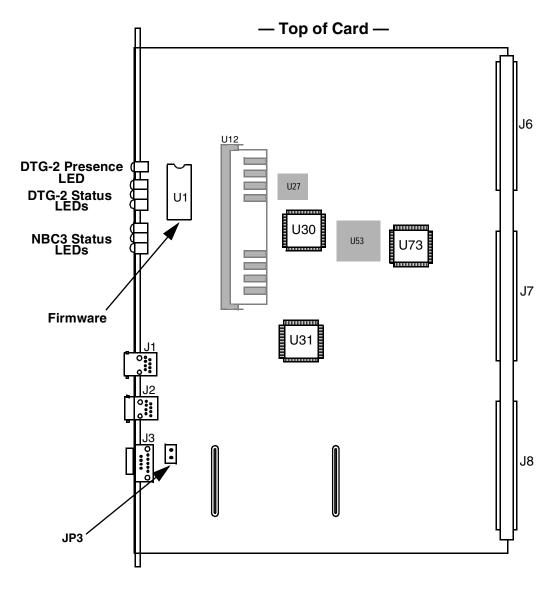

#### Network Bus Controller 3 Card (NBC3)

| Figure 1: Block Diagram of NBC3 Card                    | 3  |

|---------------------------------------------------------|----|

| Figure 2: NBC3 Card Interconnections for VCO/4K Systems | 6  |

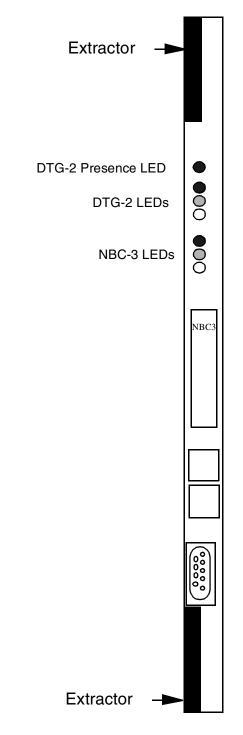

| Figure 3: NBC3 Card Front Panel                         | 7  |

| Figure 4: NBC3 (Rev E) JP3 and Firmware Location        | 11 |

| Figure 5: PCB Card Retainer Bar                         | 12 |

## **Direct Inward Dial Card (DID-2)**

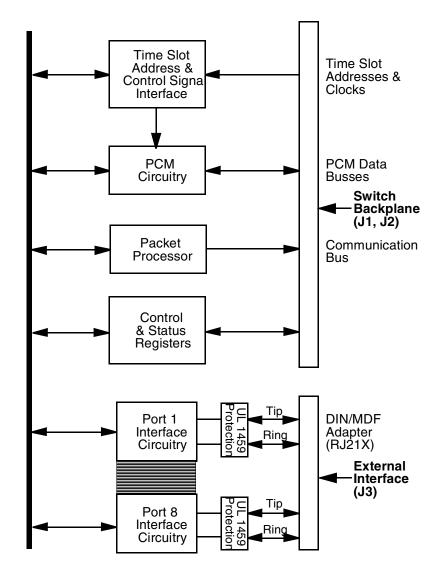

| Figure 1: Block Diagram Of DID-2 Card                                  | 4  |

|------------------------------------------------------------------------|----|

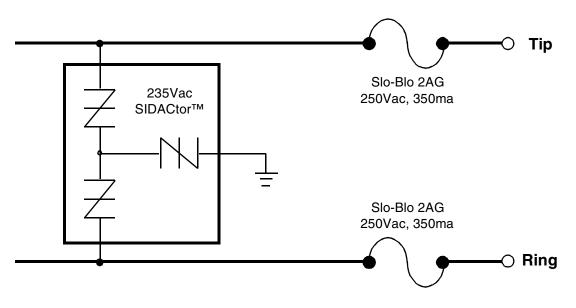

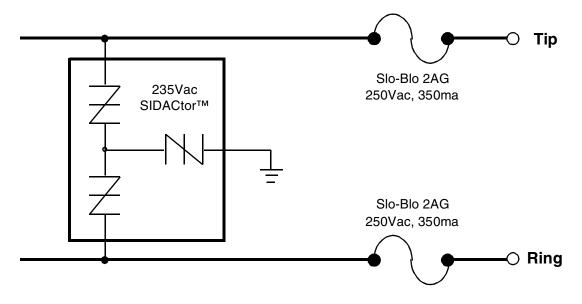

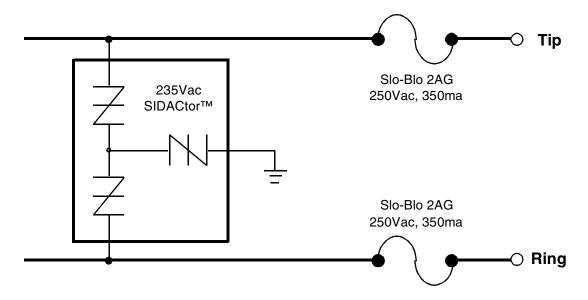

| Figure 2: Schematic Diagram Of Tip & Ring Protective Devices           | 6  |

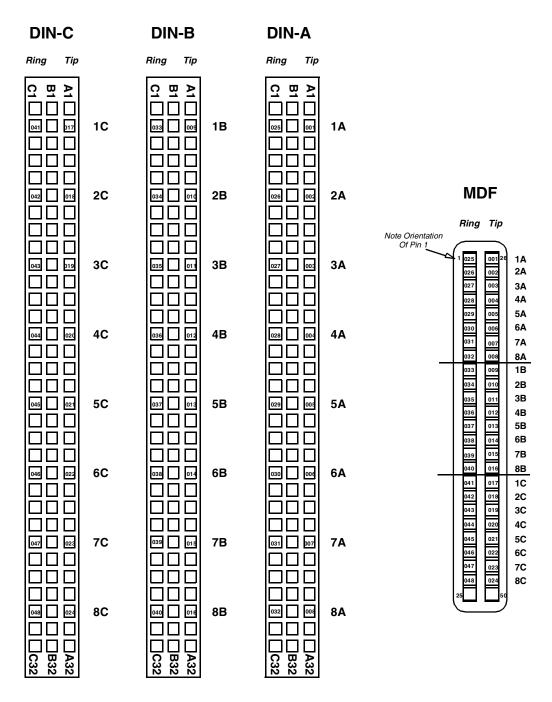

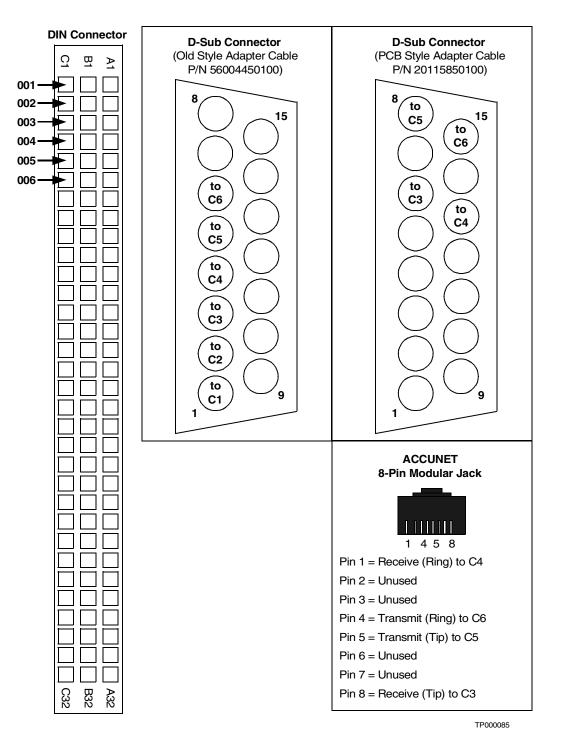

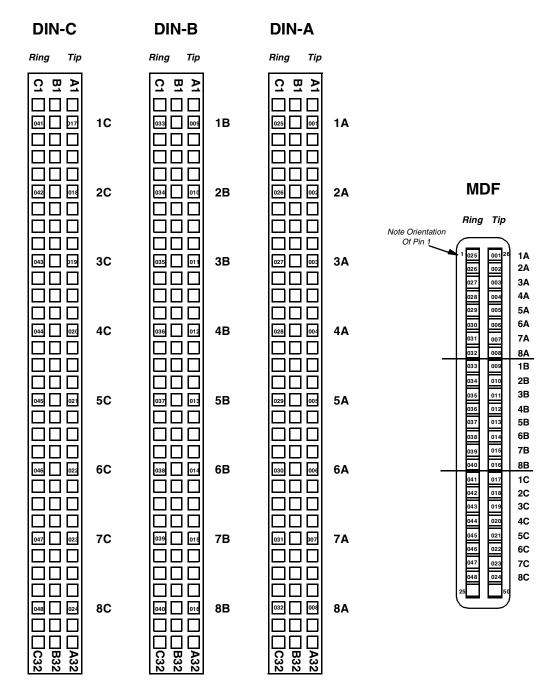

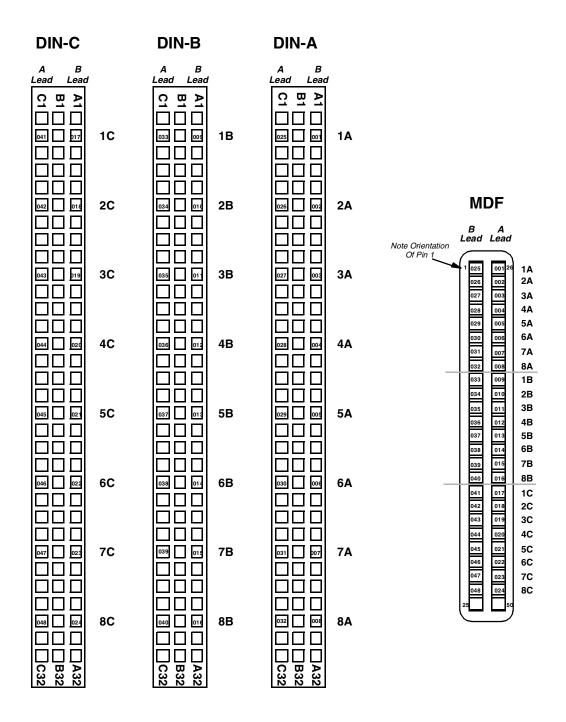

| Figure 3: Pin-Out Diagram Of DIN–RJ21X MDF Adapter                     | 12 |

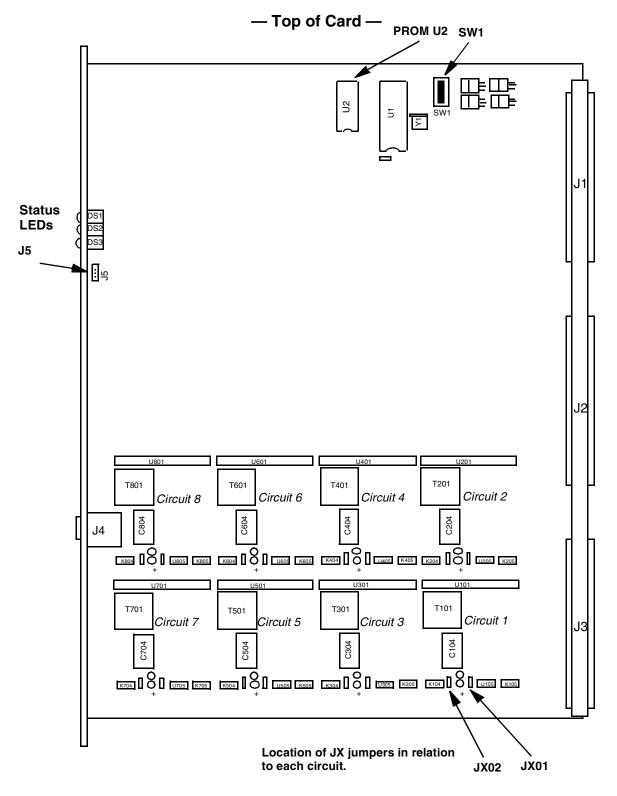

| Figure 4: DID-2 card Jumper & PROM Locations                           | 14 |

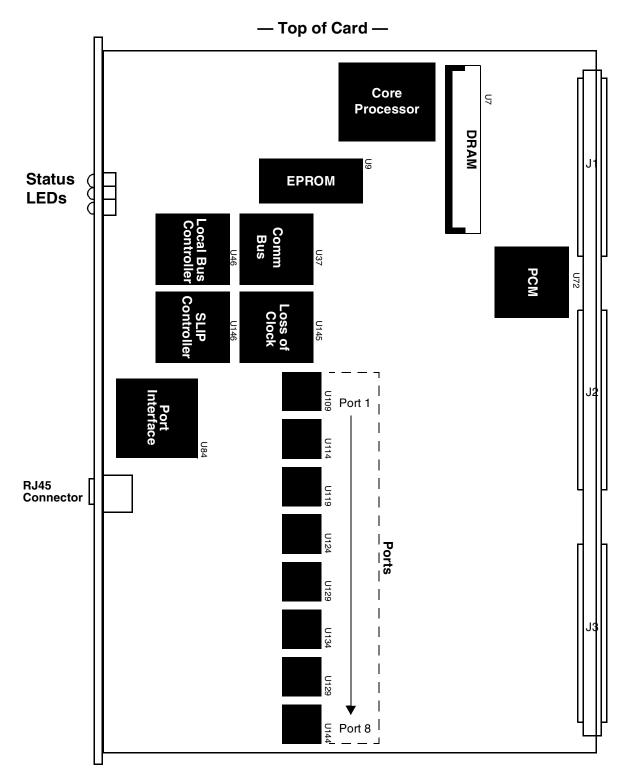

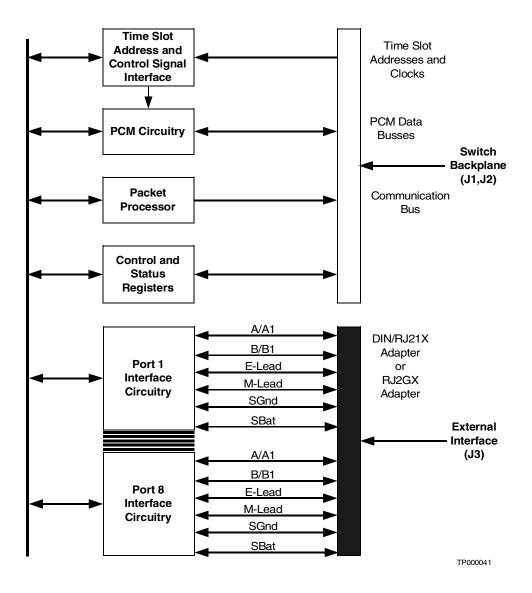

| Drop and Insert Card (D+I)                                             |    |

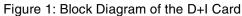

| Figure 1: Block Diagram of the D+I Card                                | 2  |

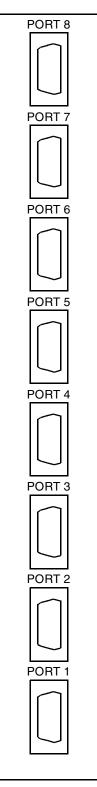

| Figure 2: D+I MDF and DB9 Pinout                                       | 6  |

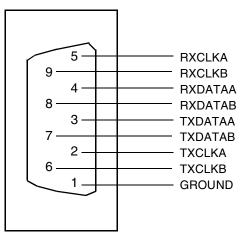

| Figure 3: Data Loopback                                                | 7  |

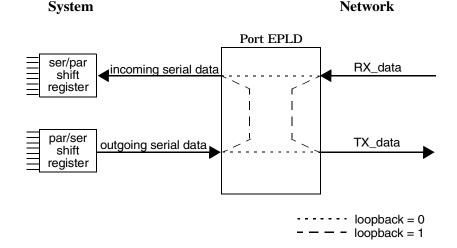

| Figure 4: D+I Card                                                     | 8  |

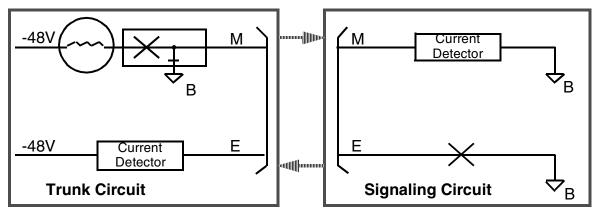

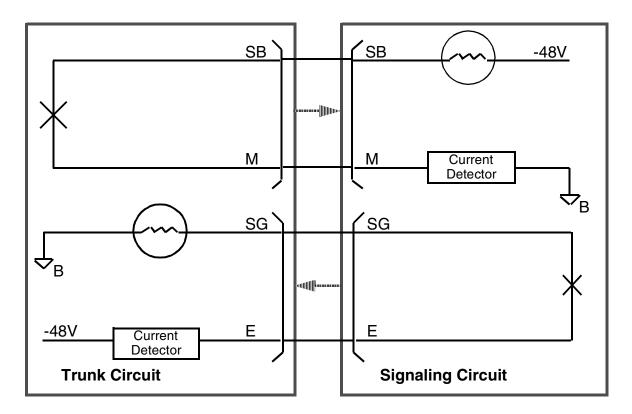

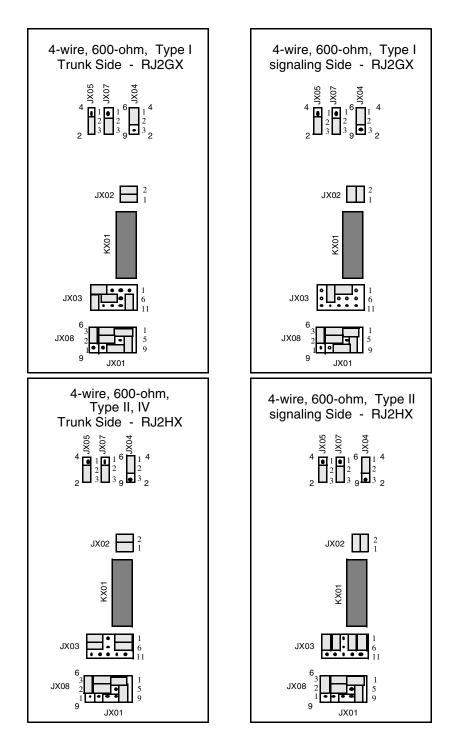

| E+M Trunk Card (E+M)                                                   |    |

| Figure 1: Block Diagram Of E+M Card                                    | 3  |

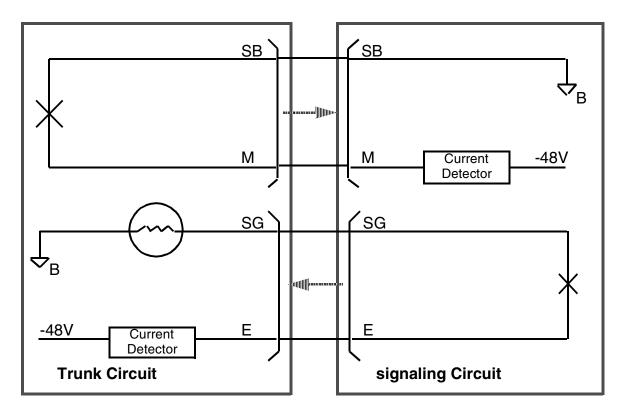

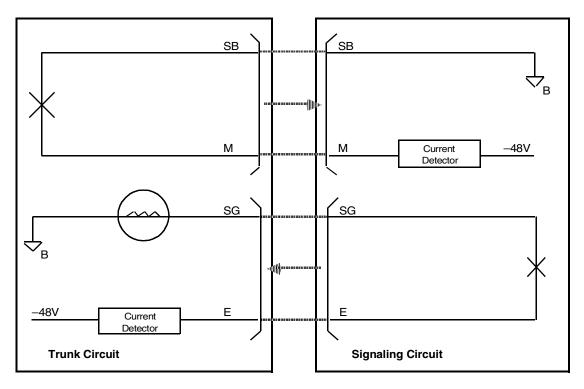

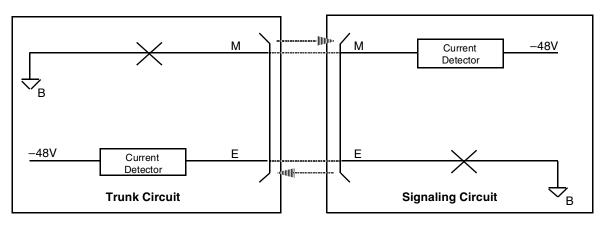

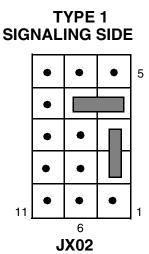

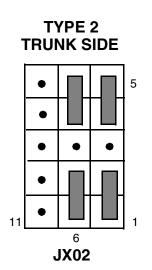

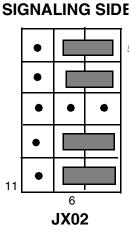

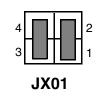

| Figure 2: E+M Type I Interface                                         | 5  |

| Figure 3: E+M Type II Interface                                        | 5  |

| Figure 4: E+M Type IV Interface                                        | 6  |

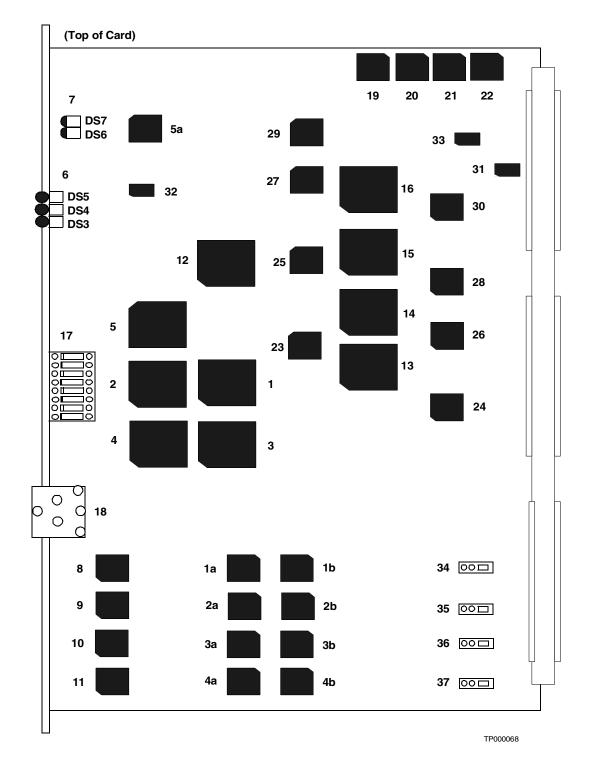

| Figure 5: E+M Type V Interface                                         | 6  |

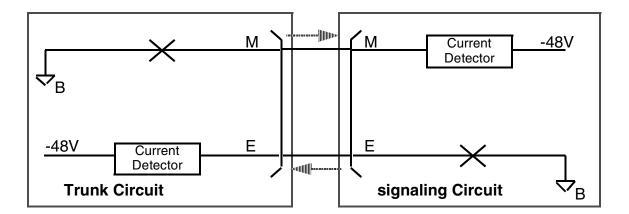

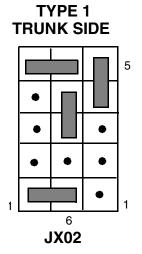

| Figure 6: E+M Jumper & PROM Locations                                  | 12 |

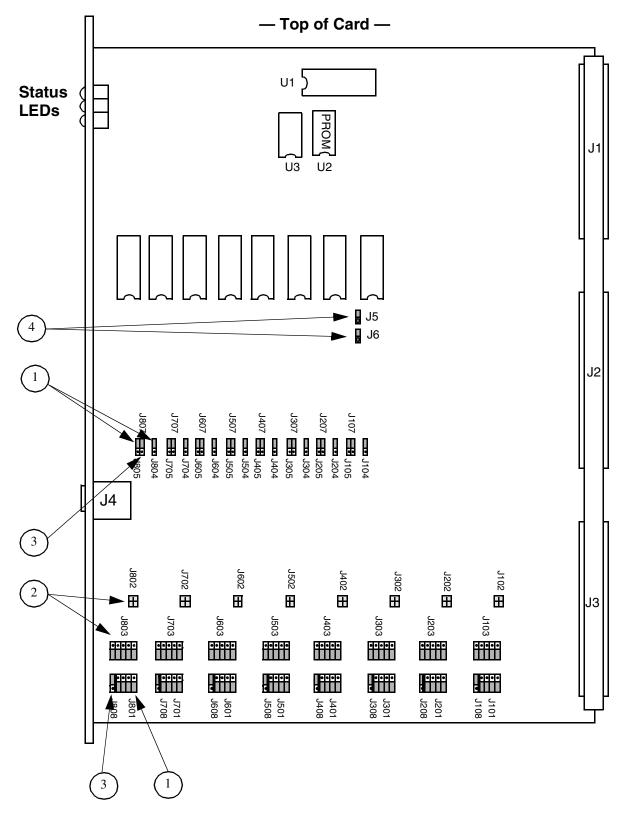

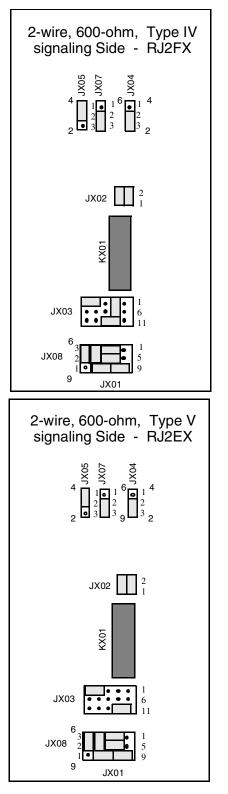

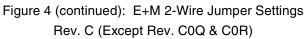

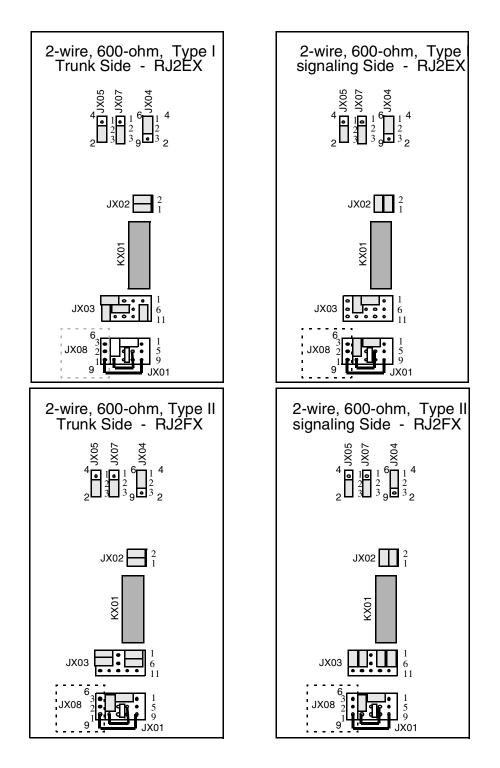

| Figure 7: E+M 2-Wire Jumper Settings<br>Rev. C (Except Rev. C0Q & C0R) | 14 |

| Figure 8: E+M 2-Wire Jumper Settings<br>Rev. C0Q, C0R & Rev. D         | 16 |

| Figure 9: E+M 4-Wire Jumper Settings, Rev. C & D                       | 18 |

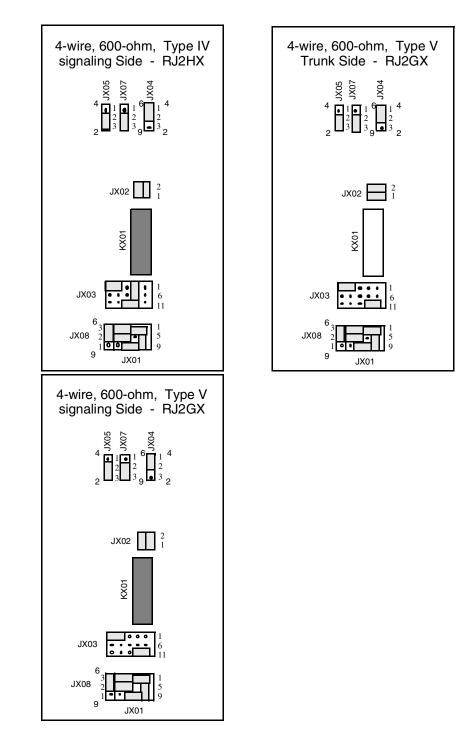

| Four Span Programmable<br>T1 Interface Card (4xT1)                     |    |

| Figure 1: Block Diagram of the Four Span T1 Card                       | 2  |

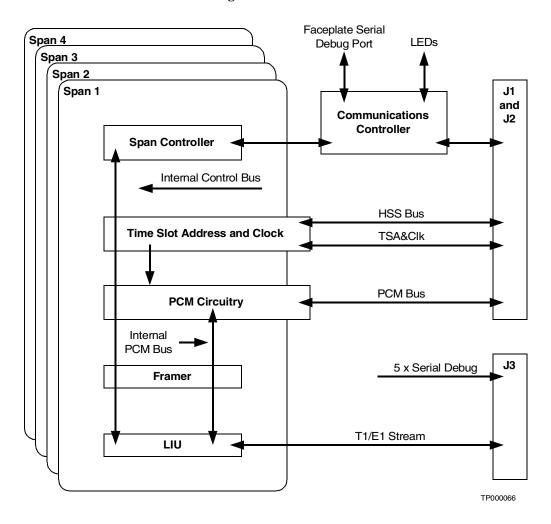

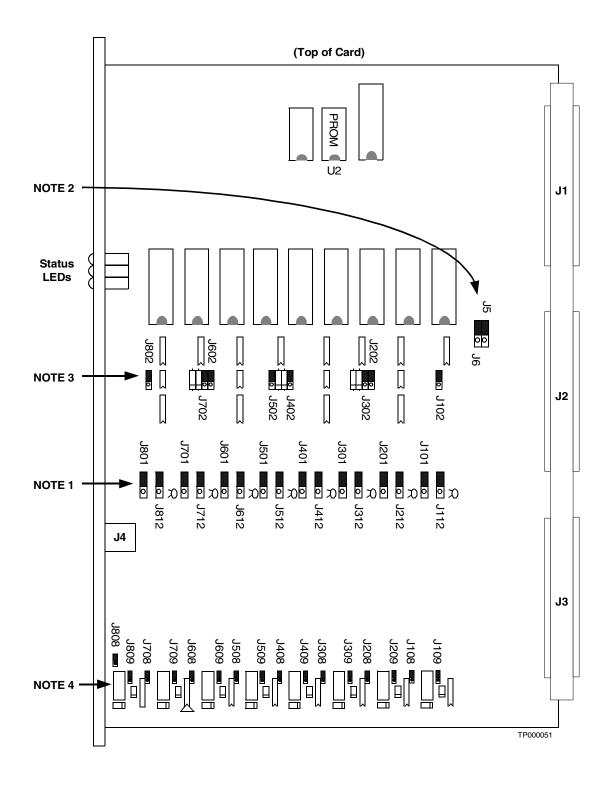

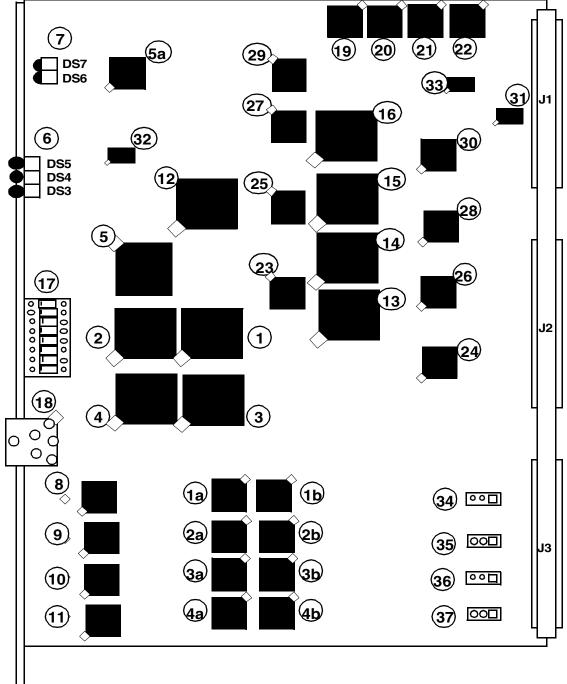

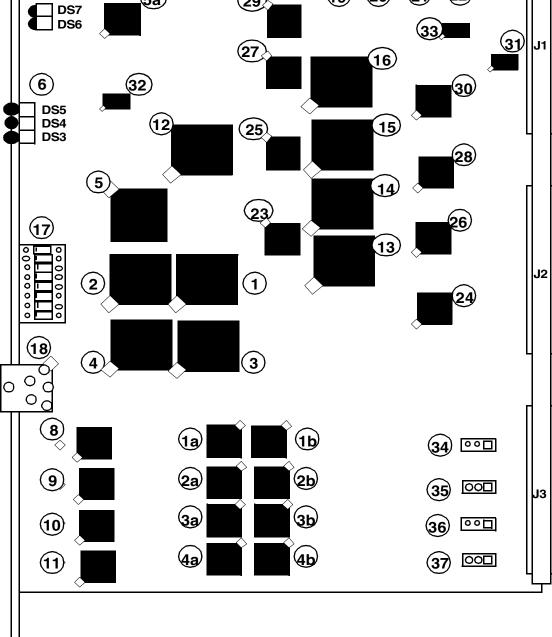

| Figure 2: Four Span T1 Interface Board Layout                          | 9  |

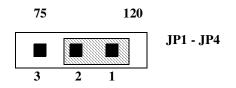

| Figure 3: JP1 through JP4 Jumper Pin Configuration                     | 12 |

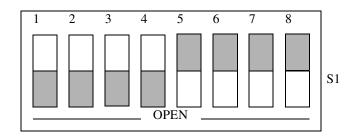

| Figure 4: µ-law Configuration Switch                                   | 13 |

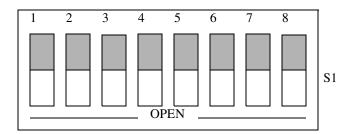

| Figure 5: A-law Configuration Switch                                   | 13 |

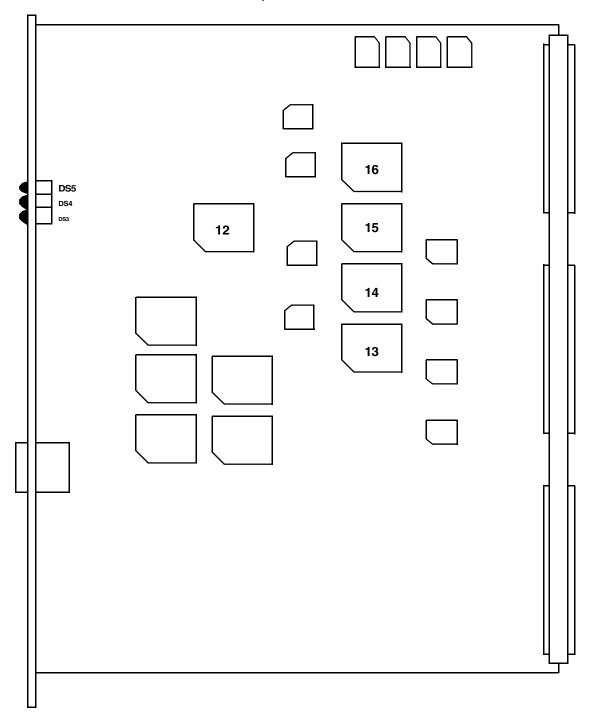

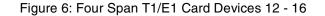

| Figure 6: Four Span T1/E1 Card Devices 12 - 16                         | 14 |

| Interface Controller Card (ICC)                                        |    |

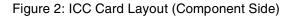

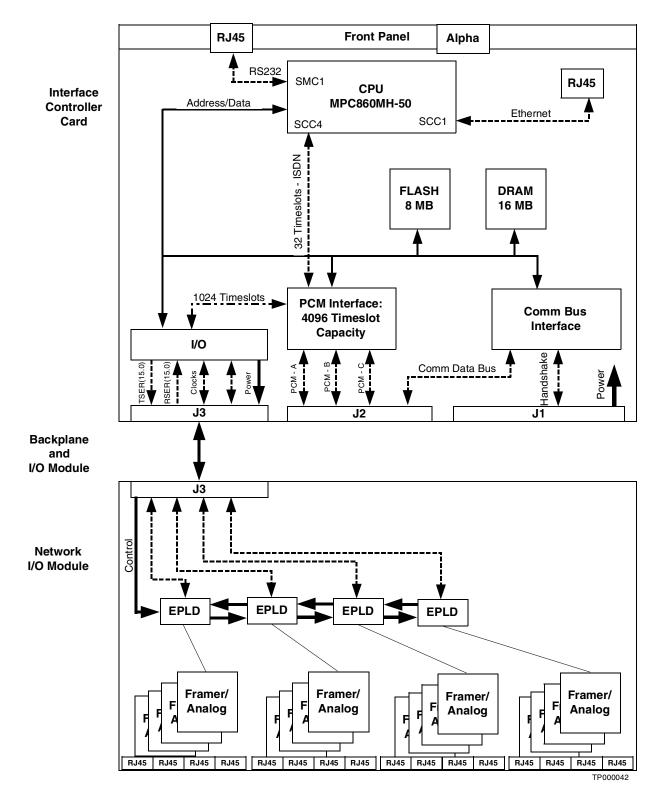

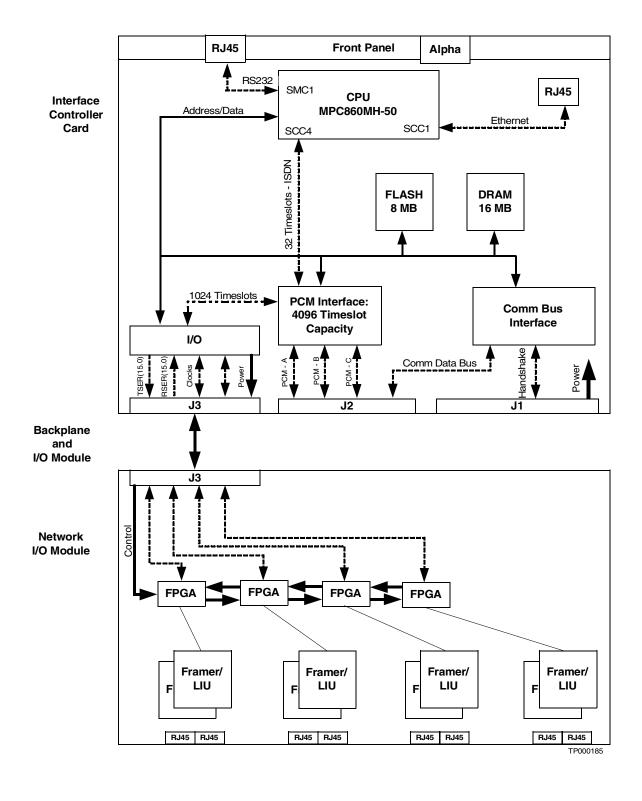

| Figure 1: ICC Card and I/O Module Architecture                         | 3  |

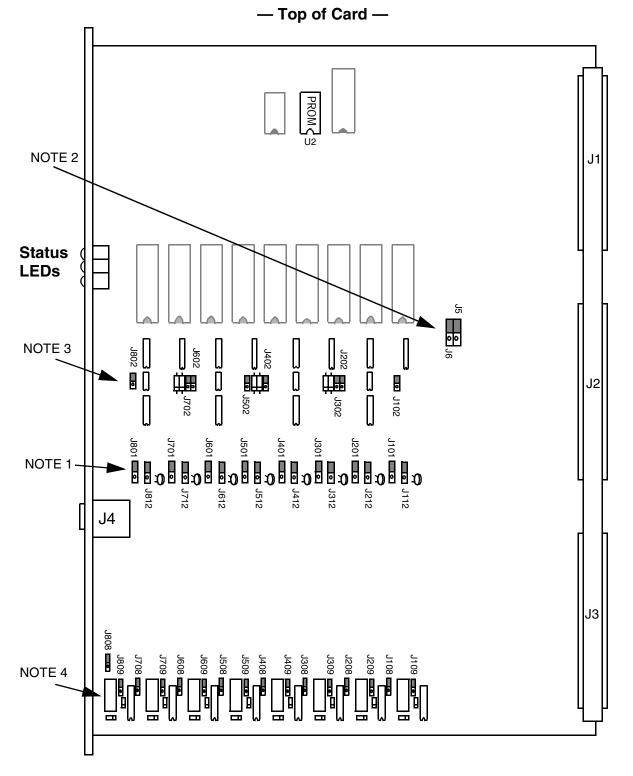

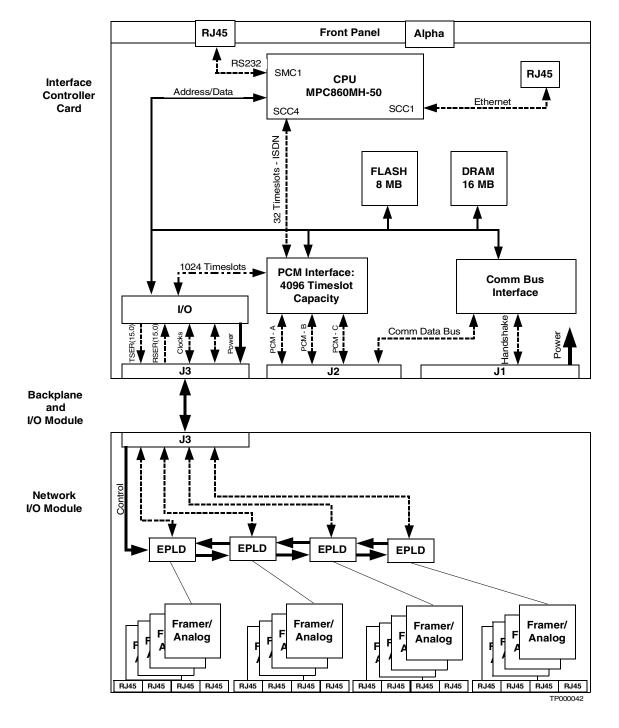

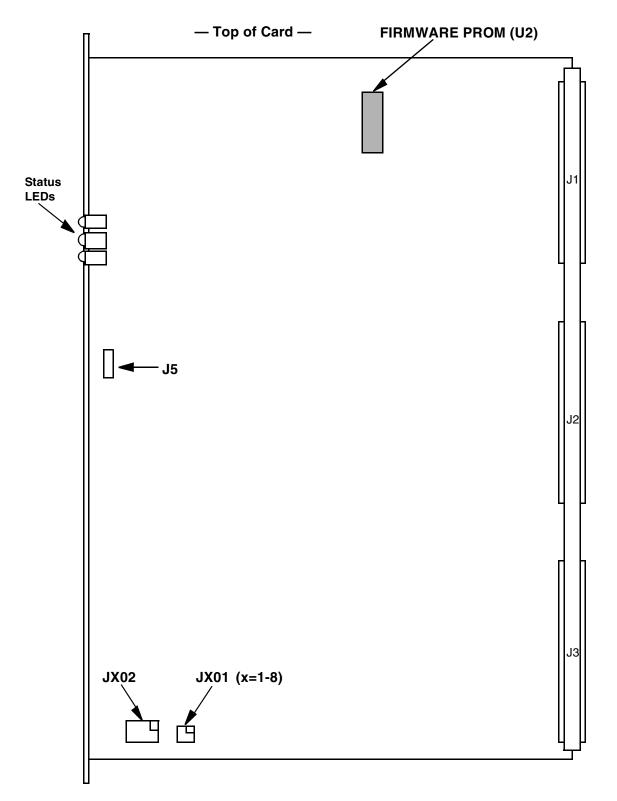

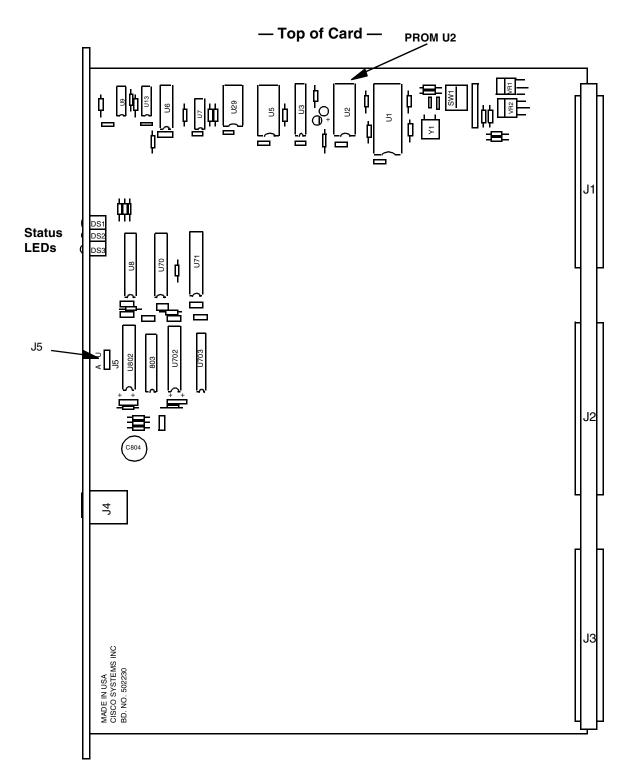

| Figure 2: ICC Card Layout (Component Side)                             | 5  |

#### Interface Controller Card T1 I/O Module

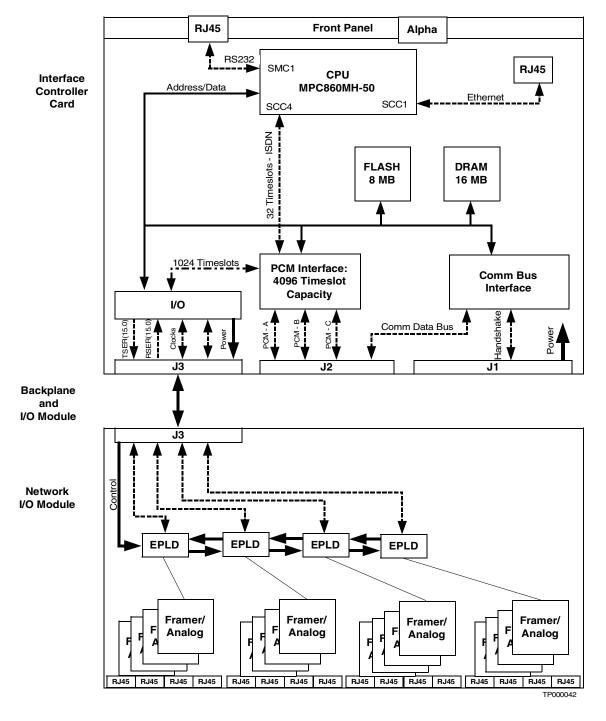

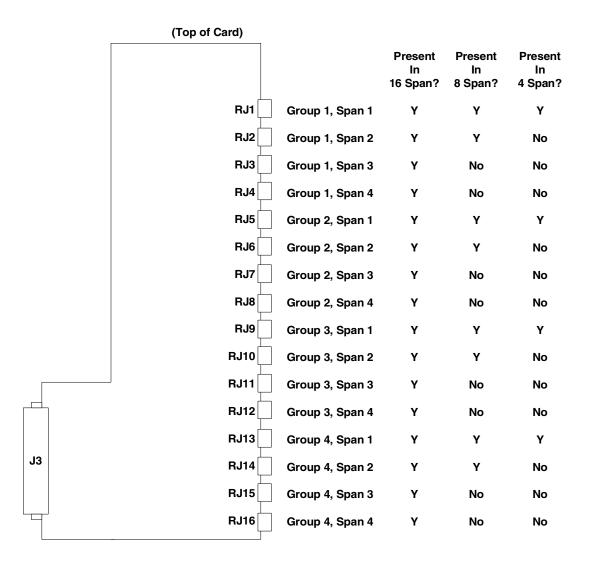

| Figure 1: ICC Card and I/O Module Architecture                 | 3  |

|----------------------------------------------------------------|----|

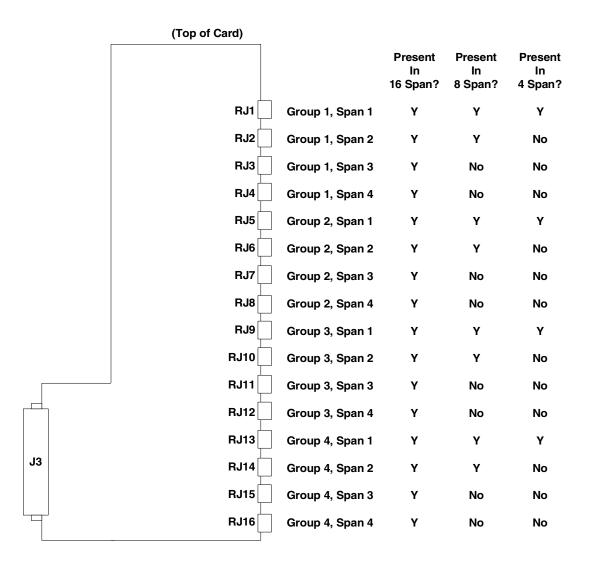

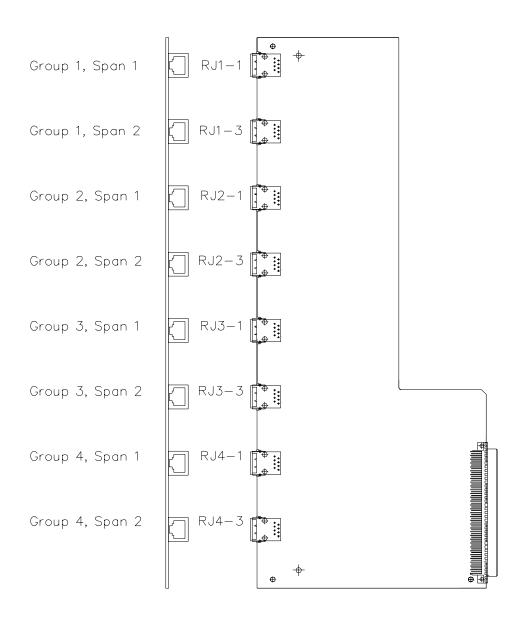

| Figure 2: I/O Module Card Layout (16-Span, Circuit Side)       | 4  |

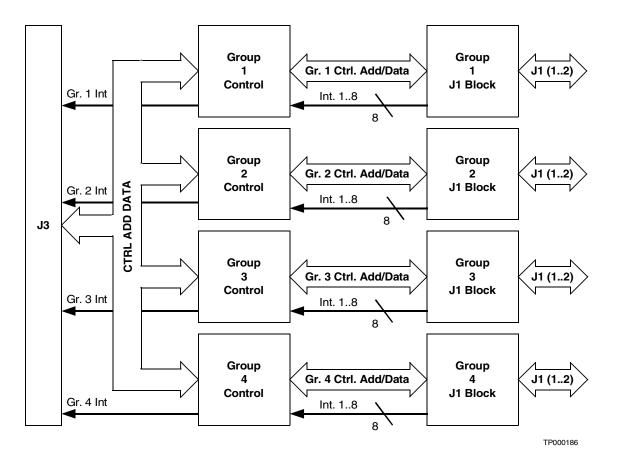

| Figure 3: 16-Span I/O Module Span Grouping                     | 6  |

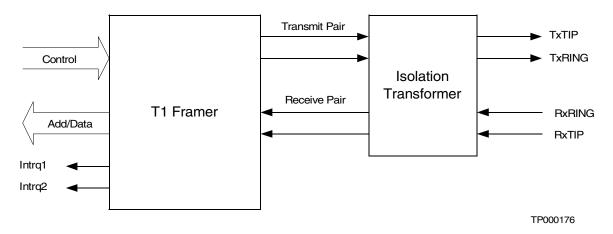

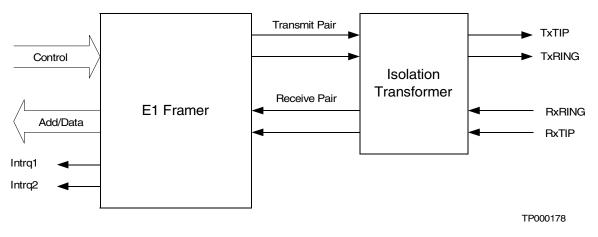

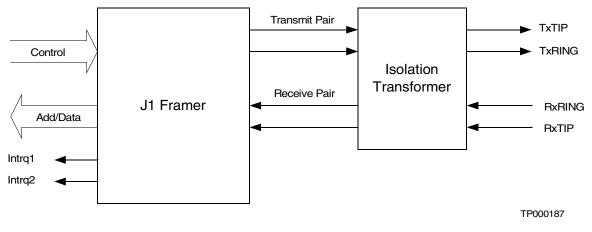

| Figure 4: Framer Block Diagram                                 | 7  |

| Line Test Card-8 (LTC-8)                                       |    |

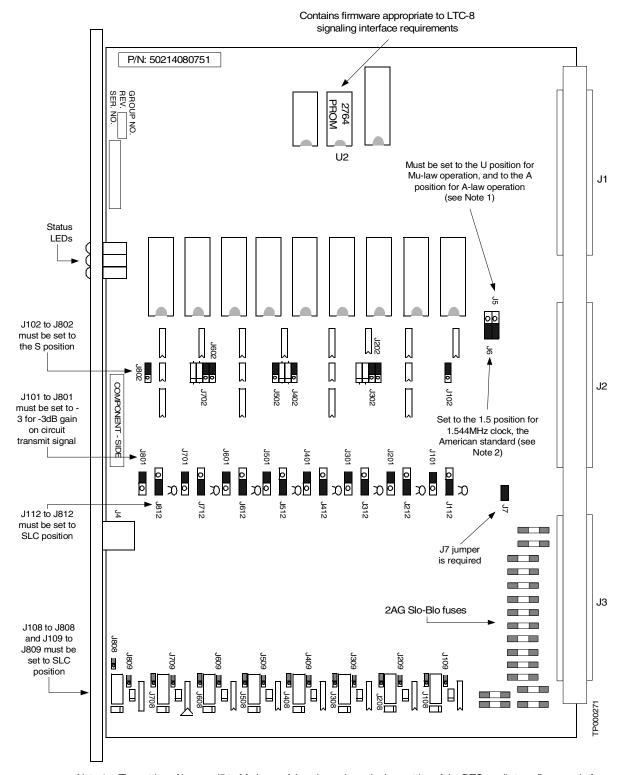

| Figure 1: LTC-8 Jumper and PROM Locations                      | 2  |

| Figure 2: J3 96-PIN DIN Connector                              | 3  |

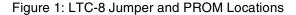

| Figure 3: Block Diagram of LTC-8                               | 7  |

| Figure 4: Schematic Diagram of Tip and Ring Protective Devices | 9  |

| MVDC Programmable T1<br>Interface Card (MVDC)                  |    |

| Figure 1: Block Diagram of the MVDC T1 Card                    | 2  |

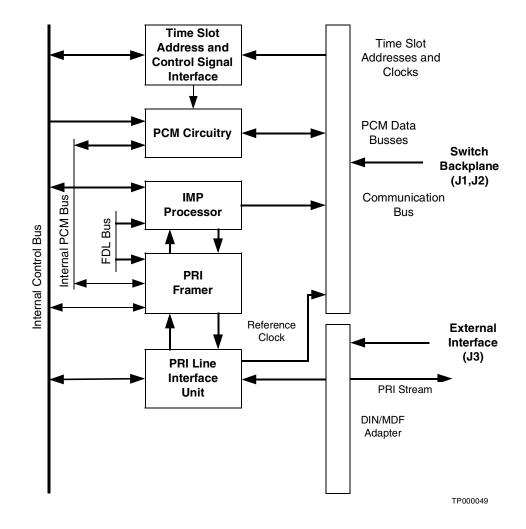

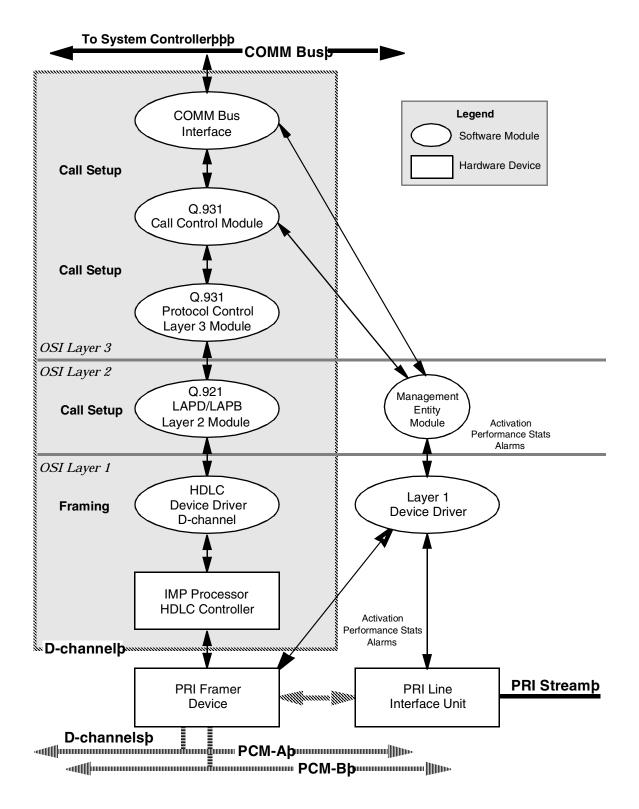

| Primary Rate Interface/NFAS Card (PRI/N)                       |    |

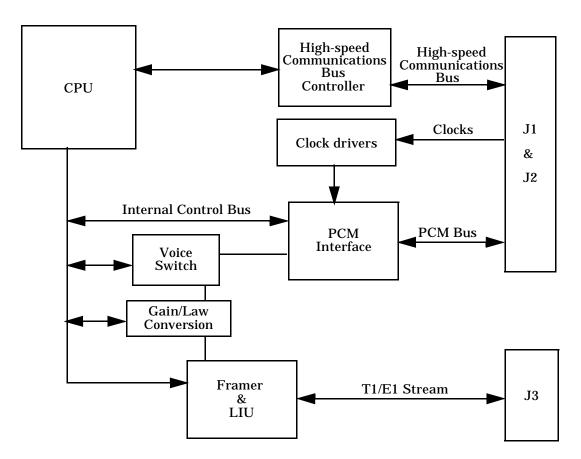

| Figure 1: Block Diagram Of PRI/N Card                          | 3  |

| Figure 2: PRI/N Card Hardware Devices & Software Modules       | 6  |

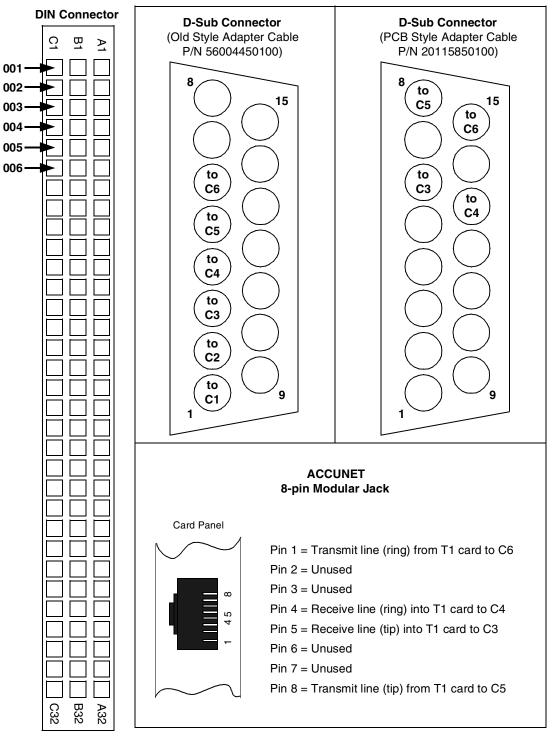

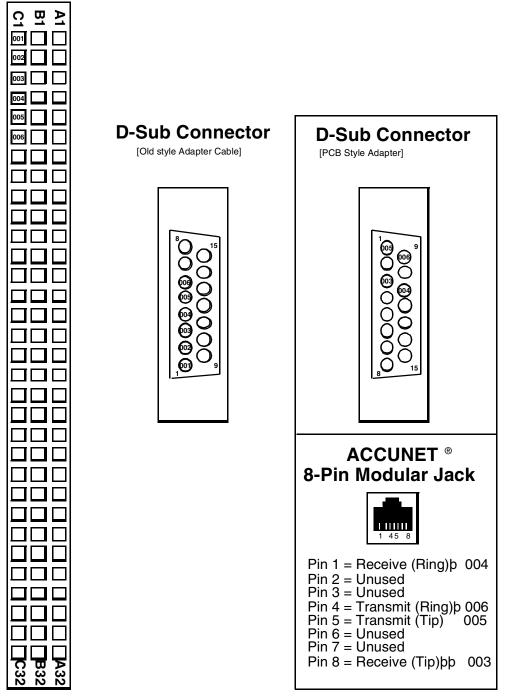

| Figure 3: Pin Out diagram of T1 & PRI/N Adapters               | 14 |

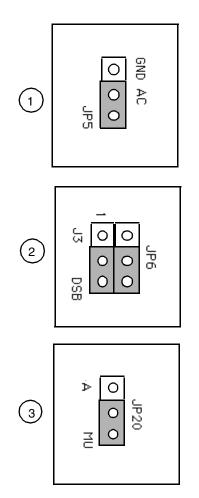

| Figure 4: PRI/N Card Jumper Locations                          | 17 |

| Figure 5: PRI/N Jumper Settings                                | 18 |

| Subscriber Line Interface Card (SLIC-2)                        |    |

| Figure 1: Block Diagram Of SLIC-2                              | 3  |

| Figure 2: Schematic Diagram Of Tip & Ring Protective Devices   | 5  |

| Figure 3: Pin-Out Diagram Of DIN–RJ21X MDF Adapter             | 10 |

| Figure 4: SLIC-2 Jumper & PROM Locations                       | 12 |

| T1 Interface Card (T1)                                         |    |

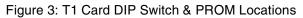

| Figure 1: T1 Card Block Diagram                                | 3  |

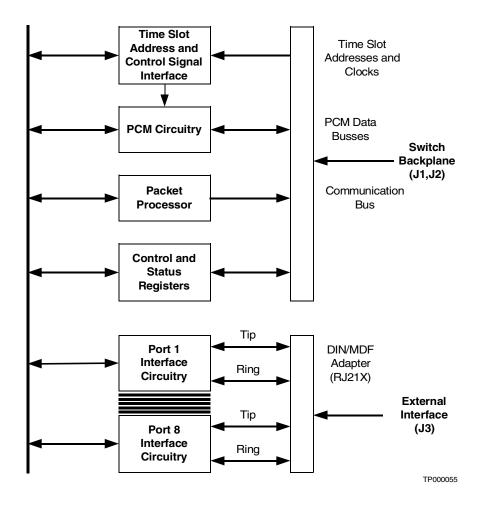

| Figure 2: T1 Adapter Pinout Diagram                            | 10 |

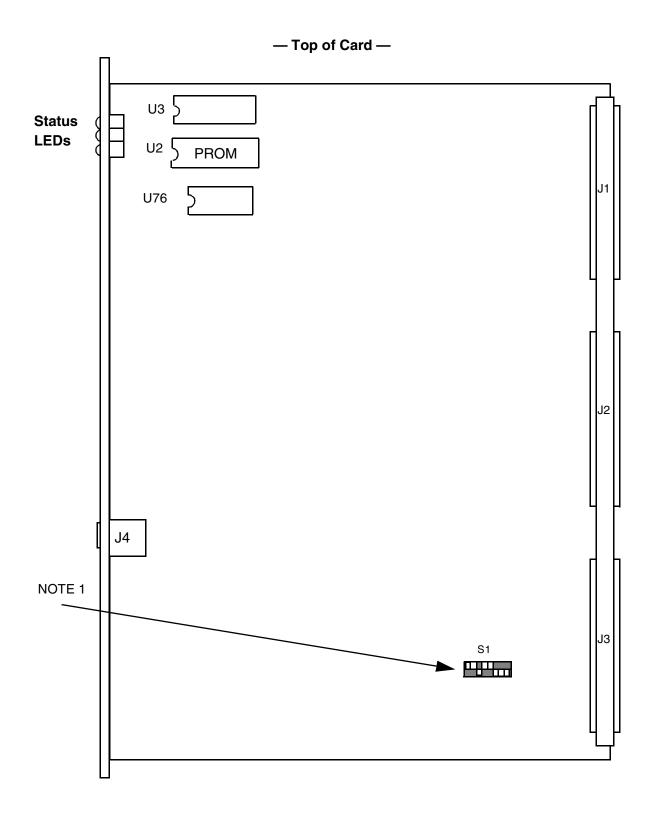

| Figure 3: T1 Card DIP Switch & PROM Locations                  | 12 |

| Universal Trunk Card (UTC-2)                                   |    |

| Figure 1: Block Diagram Of UTC-2                               | 3  |

| Figure 2: Schematic Diagram Of Tip & Ring Protective Devices   | 6  |

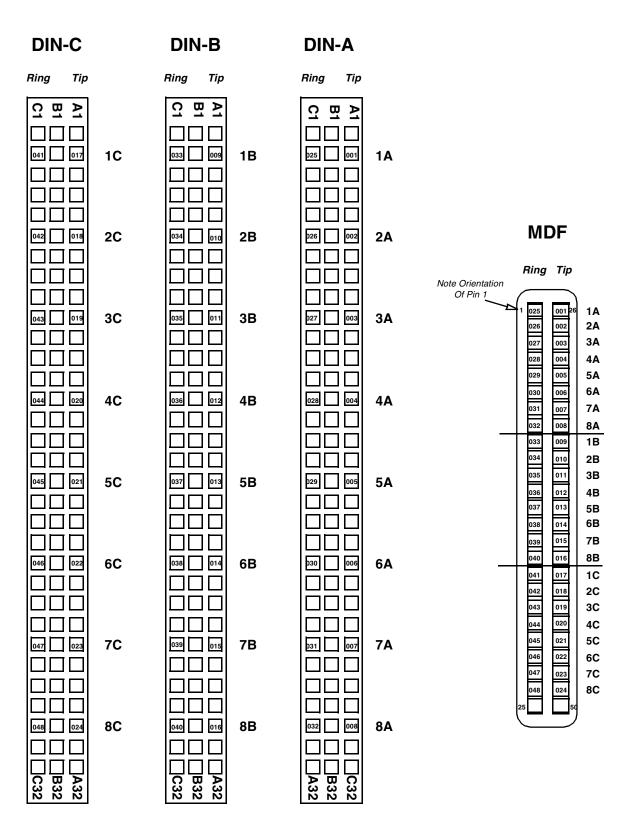

| Figure 3: Pin-Out Diagram of DIN-RJ21X MDF Adapter           | 12 |

|--------------------------------------------------------------|----|

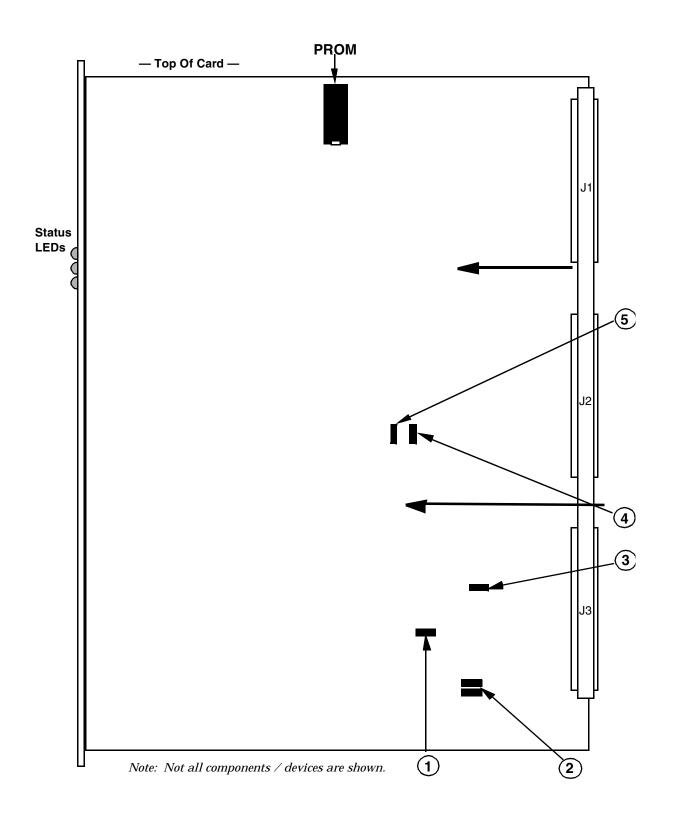

| Figure 4: UTC-2 Jumper & Prom Locations                      | 14 |

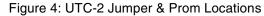

| Figure 5: Default Jumper Positions for UTC-2                 | 16 |

| Call Progress Analyzer Card (CPA)                            |    |

| Figure 1: Block Diagram Of CPA                               | 3  |

| Figure 2: CPA Jumper & PROM Locations                        | 6  |

| Digital Conference Card (DCC)                                |    |

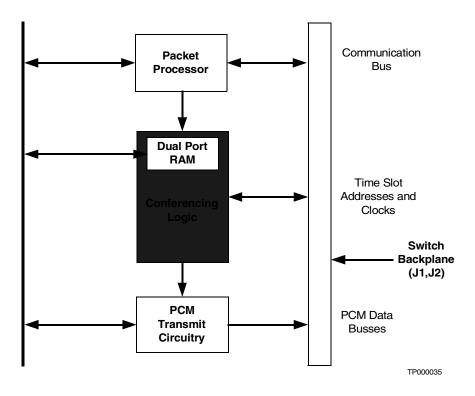

| Figure 1: Block Diagram Of DCC                               | 2  |

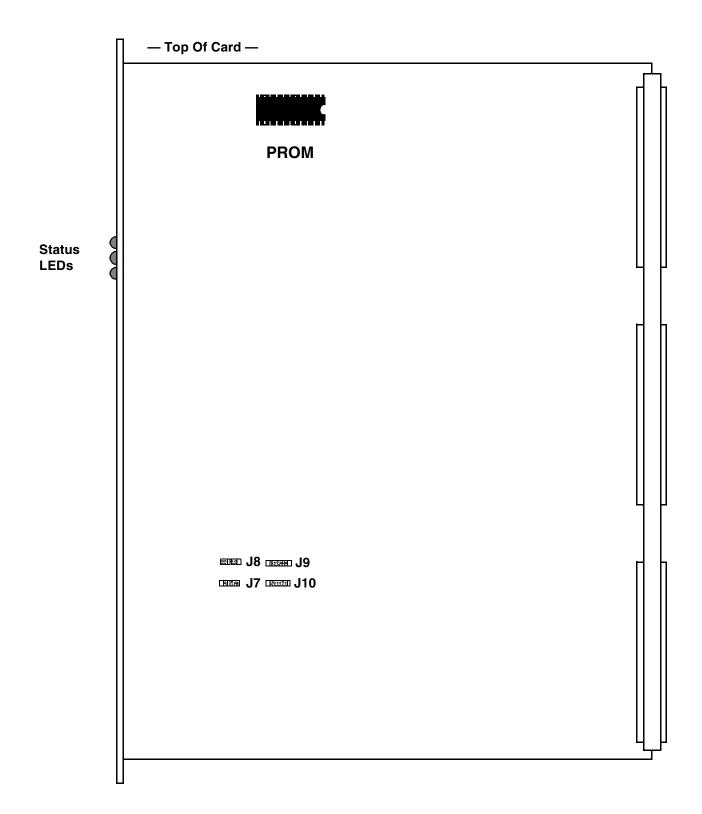

| Figure 2: DCC Jumper and PROM Locations                      | 7  |

| Digital Tone Generator Card (DTG)                            |    |

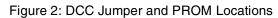

| Figure 1: DTG Block Diagram                                  | 4  |

| Figure 2: DTG PROM Locations                                 | 9  |

| Digital Tone Generator 2 Card (DTG-2)                        |    |

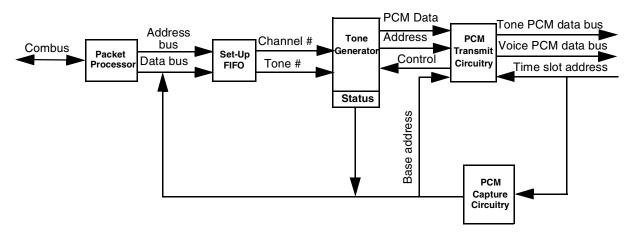

| Figure 1: DTG-2 Block Diagram                                | 2  |

| Figure 2: DTG-2 LEDs Visible From The NBC-3 Card Front Panel | 6  |

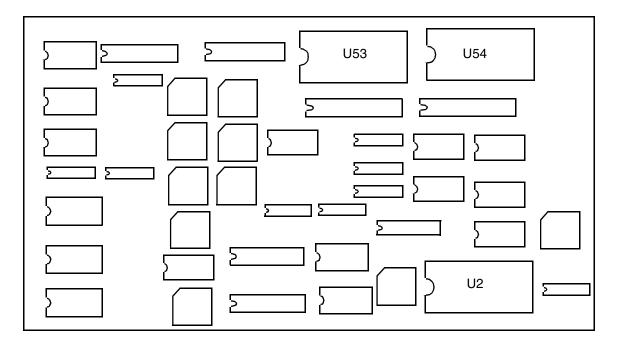

| Figure 3: DTG-2 PROM Locations                               | 7  |

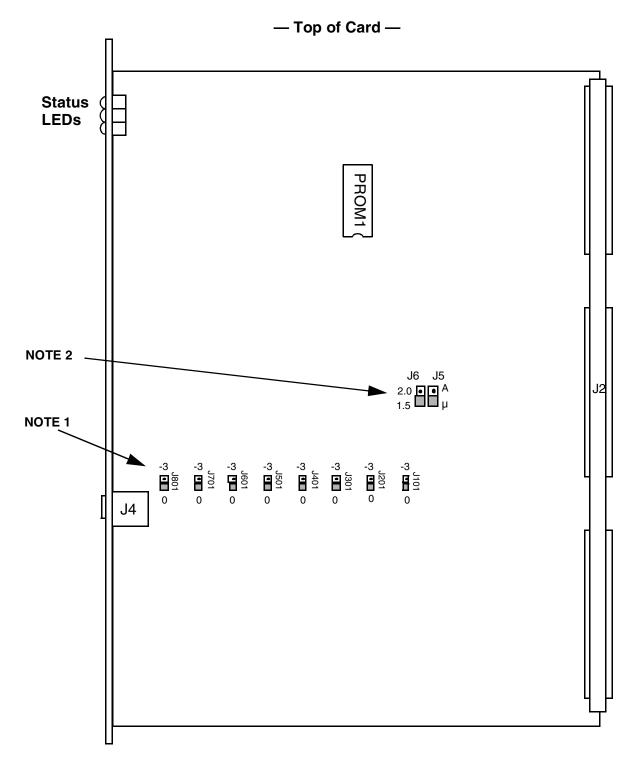

| DTMF Receiver Card (DRC-8)                                   |    |

| Figure 1: Block Diagram Of DRC                               | 2  |

| Figure 2: DRC Jumper & PROM Locations                        | 6  |

| INTEGRATED PROMPT/RECORD CARD (IPRC)                         |    |

| Figure 1: IPRC Functional Block Diagram                      | 3  |

| Figure 2: IPRC Jumper and EPROM Locations                    | 8  |

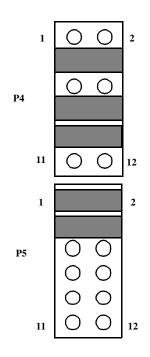

| Figure 3: P4 and P5 Jumper Placement                         | 9  |

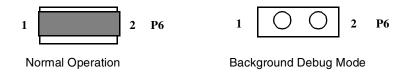

| Figure 4: P6 Jumper Placement                                | 10 |

| MF Receiver Card (MRC)                                       |    |

| Figure 1: Block Diagram Of MRC                               | 2  |

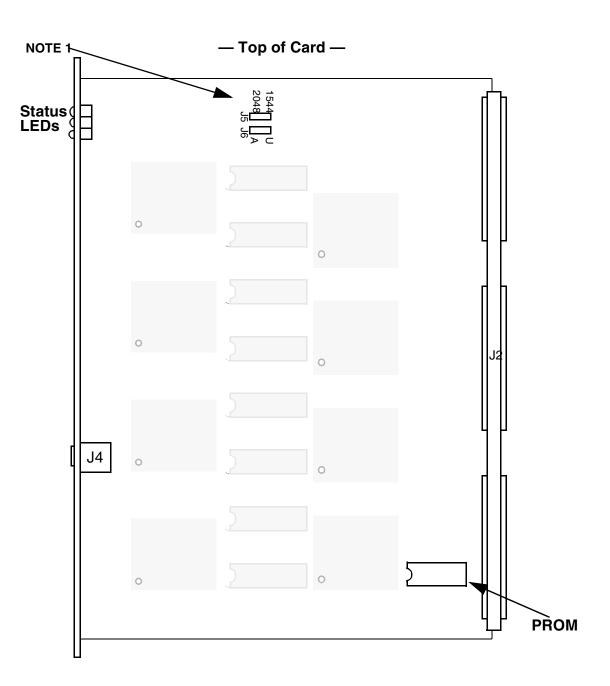

| Figure 2: MRC Jumper & PROM Locations<br>Rev. A or B         | 6  |

# DTMF Receiver Cards (DRC-24 and DRC-48)

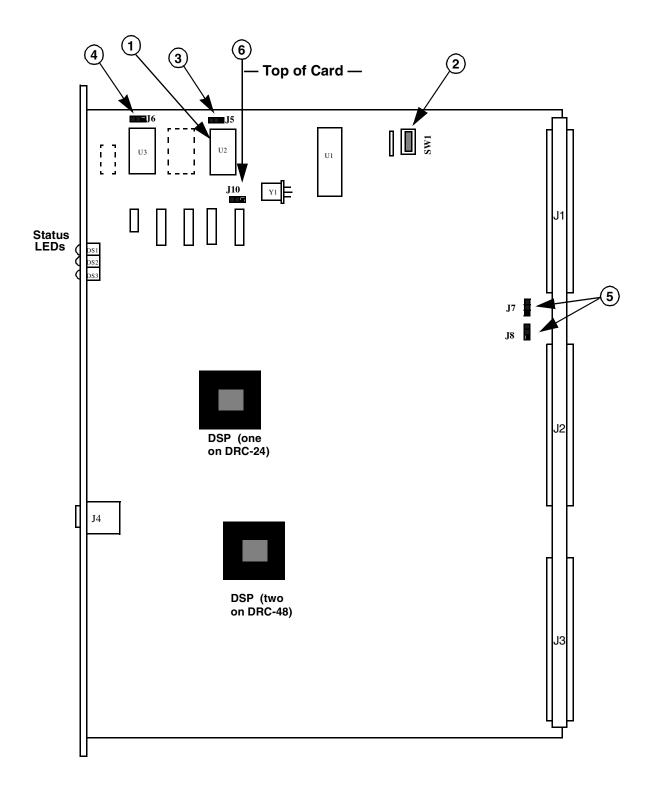

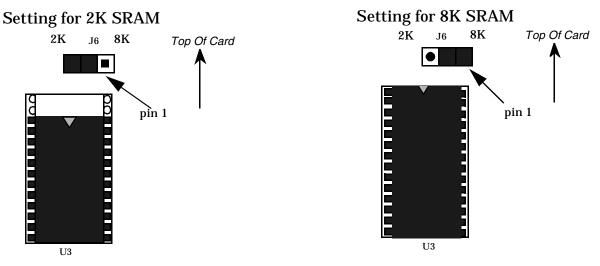

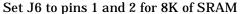

| Figure 2: DRC-24 and DRC-48 Jumper and PROM Locations<br>Subrate Switching Card (SSC)<br>Figure 1: Subrate Switching Card Board Layout<br>Service Platform Card (SPC)<br>Figure 1: SPC Card and SRM Module Block Diagram<br>Figure 2: SPC Card Layout (Component Side)<br>Figure 3: HDLC Command/Control Processor Arrangement<br>Figure 4: Securing the SRM<br>Direct Dial Inward Card (DDI)<br>Figure 2: Schematic Diagram Of DDI Card<br>Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN-RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1/CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pin-Out Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of DIN-RJ21X Connector<br>Figure 3: Pin-Out Diagram Of DIN-RJ21X Connector<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of DIN-RJ21X Connector<br>Figure 3: Pin-Out Diagram Of DIN-RJ21X Connector<br>Figure 4: E1-CAS Card Jumper & PROM Locations<br>International E+M Trunk Card<br>(E+M/DC5) | Figure 1   | : Block Diagram of DRC-24 and DRC-48                       | 2  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------|----|

| Figure 1: Subrate Switching Card Board Layout<br>Service Platform Card (SPC)<br>Figure 1: SPC Card and SRM Module Block Diagram<br>Figure 2: SPC Card Layout (Component Side)<br>Figure 3: HDLC Command/Control Processor Arrangement<br>Figure 4: Securing the SRM<br>Direct Dial Inward Card (DDI)<br>Figure 1: Block Diagram Of DDI Card<br>Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN–RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1/CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of DIN–RJ21X Connector<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations                                                                                                                                                                                                                                                                                                                                              | Figure 2   | : DRC-24 and DRC-48 Jumper and PROM Locations              | 6  |

| Service Platform Card (SPC)<br>Figure 1: SPC Card and SRM Module Block Diagram<br>Figure 2: SPC Card Layout (Component Side)<br>Figure 3: HDLC Command/Control Processor Arrangement<br>Figure 4: Securing the SRM<br>Direct Dial Inward Card (DDI)<br>Figure 1: Block Diagram Of DDI Card<br>Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN-RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN-RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                           | Subrate S  | witching Card (SSC)                                        |    |

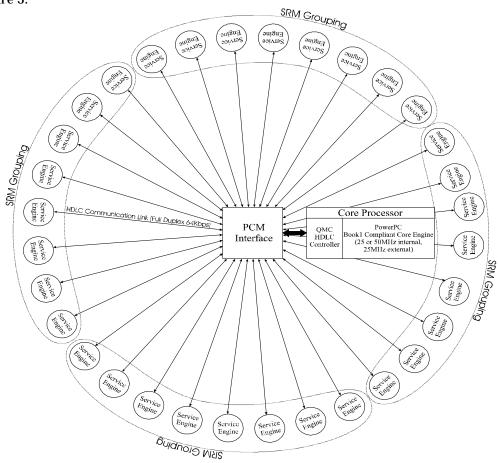

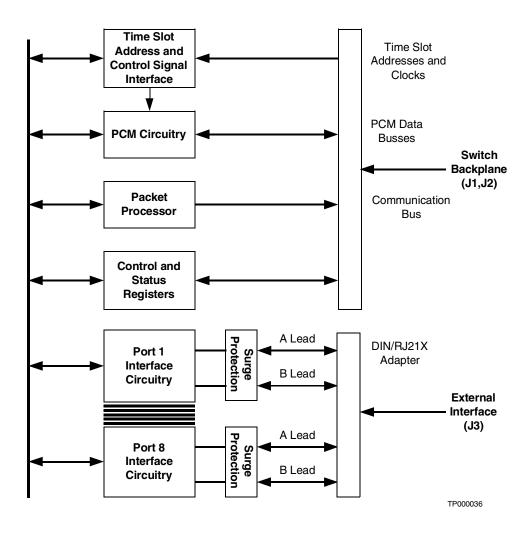

| Figure 1:       SPC Card and SRM Module Block Diagram         Figure 2:       SPC Card Layout (Component Side)         Figure 3:       HDLC Command/Control Processor Arrangement         Figure 4:       Securing the SRM         Direct Dial Inward Card (DDI)       Figure 1:         Figure 2:       Schematic Diagram Of DDI Card         Figure 3:       Pin-Out Diagram Of A & B Lead Protective Devices         Figure 3:       Pin-Out Diagram Of DIN-RJ21X MDF Adapter         Figure 4:       DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224         E1-Channel Associated       Signalling Card (E1-CAS)         Figure 1:       Block Diagram of E1-CAS Card         Figure 2:       CAS Multiframe Format         Figure 3:       Pinout Diagram of E1/E1-PRI Adapters         Figure 4:       E1-CAS Card Jumper Locations         Earth/Loop Connect Trunk Card       (ECT/LCT)         Figure 1:       Block Diagram Of ECT/LCT         Figure 2:       Pin-Out Diagram Of DIN-RJ21X Connector         Figure 3:       ECT/LCT Jumper & PROM Locations                                                                                                                                                                                                                                   | Figure 1   | : Subrate Switching Card Board Layout                      | 3  |

| Figure 2: SPC Card Layout (Component Side)         Figure 3: HDLC Command/Control Processor Arrangement         Figure 4: Securing the SRM         Direct Dial Inward Card (DDI)         Figure 1: Block Diagram Of DDI Card         Figure 2: Schematic Diagram Of A & B Lead Protective Devices         Figure 3: Pin-Out Diagram Of DIN-RJ21X MDF Adapter         Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224         E1-Channel Associated         Signalling Card (E1-CAS)         Figure 1: Block Diagram of E1-CAS Card         Figure 2: CAS Multiframe Format         Figure 3: Pinout Diagram of E1/E1-PRI Adapters         Figure 4: E1-CAS Card Jumper Locations         Earth/Loop Connect Trunk Card         (ECT/LCT)         Figure 1: Block Diagram Of ECT/LCT         Figure 2: Pin-Out Diagram Of DIN-RJ21X Connector         Figure 3: ECT/LCT Jumper & PROM Locations         International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                              | Service P  | atform Card (SPC)                                          |    |

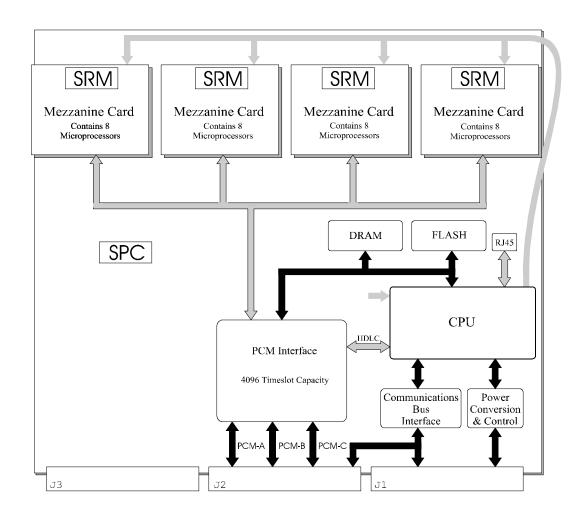

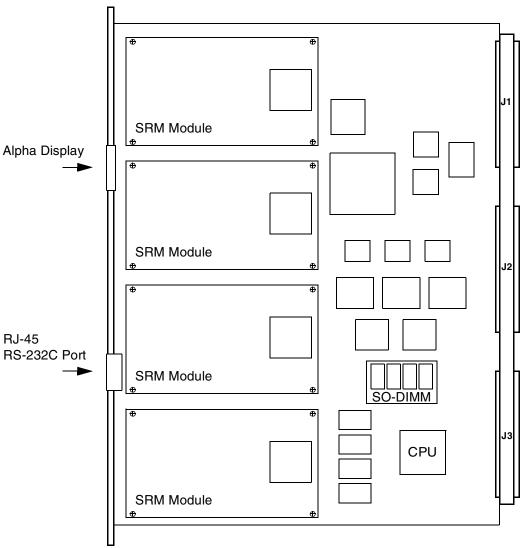

| Figure 3: HDLC Command/Control Processor Arrangement<br>Figure 4: Securing the SRM<br>Direct Dial Inward Card (DDI)<br>Figure 1: Block Diagram Of DDI Card<br>Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN–RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 1   | : SPC Card and SRM Module Block Diagram                    | 3  |

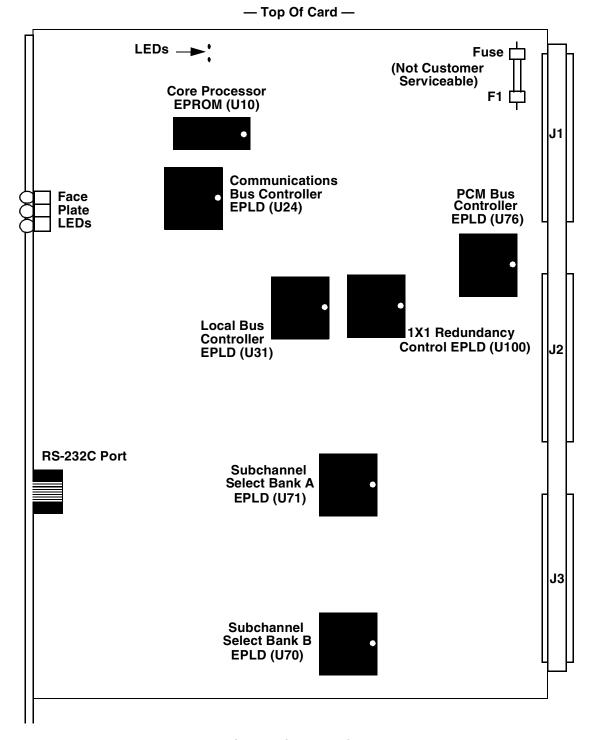

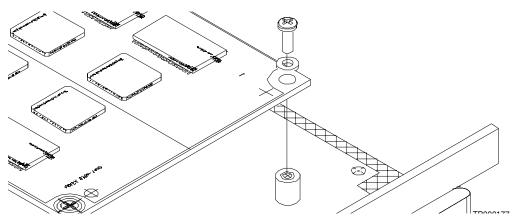

| Figure 4: Securing the SRM<br>Direct Dial Inward Card (DDI)<br>Figure 1: Block Diagram Of DDI Card<br>Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN-RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN-RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 2   | : SPC Card Layout (Component Side)                         | 4  |

| Direct Dial Inward Card (DDI)<br>Figure 1: Block Diagram Of DDI Card<br>Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN-RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN-RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 3   | : HDLC Command/Control Processor Arrangement               | 5  |

| Figure 1: Block Diagram Of DDI Card<br>Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN-RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN-RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 4   | : Securing the SRM                                         | 11 |

| Figure 2: Schematic Diagram Of A & B Lead Protective Devices<br>Figure 3: Pin-Out Diagram Of DIN–RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Direct Dia | I Inward Card (DDI)                                        |    |

| Figure 3: Pin-Out Diagram Of DIN–RJ21X MDF Adapter<br>Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224<br>E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 1   | : Block Diagram Of DDI Card                                | 3  |

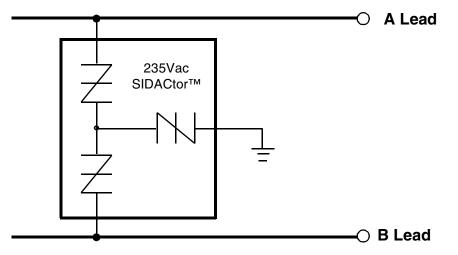

| Figure 4: DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224 E1-Channel Associated Signalling Card (E1-CAS) Figure 1: Block Diagram of E1-CAS Card Figure 2: CAS Multiframe Format Figure 3: Pinout Diagram of E1/E1-PRI Adapters Figure 4: E1-CAS Card Jumper Locations Earth/Loop Connect Trunk Card (ECT/LCT) Figure 1: Block Diagram Of ECT/LCT Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector Figure 3: ECT/LCT Jumper & PROM Locations International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 2   | : Schematic Diagram Of A & B Lead Protective Devices       | 5  |

| E1-Channel Associated<br>Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN-RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 3   | : Pin-Out Diagram Of DIN–RJ21X MDF Adapter                 | 10 |

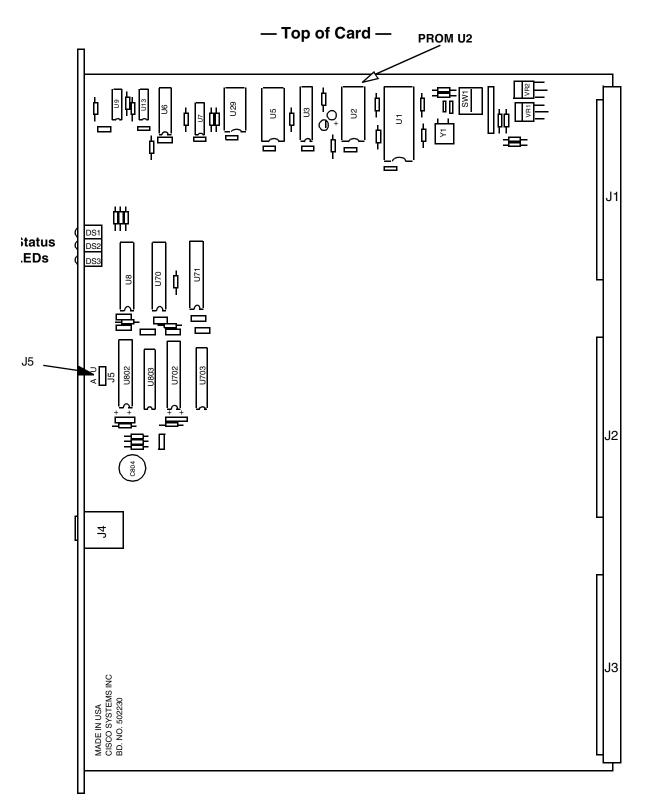

| Signalling Card (E1-CAS)<br>Figure 1: Block Diagram of E1-CAS Card<br>Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 4   | : DDI Card J5 Jumper & U2 PROM Locations — P/N 50223080224 | 12 |

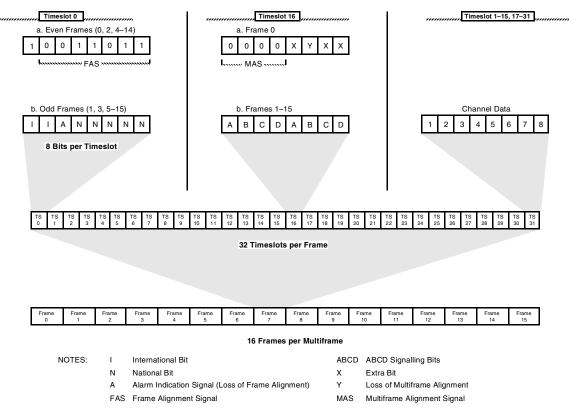

| Figure 2: CAS Multiframe Format<br>Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                            |    |

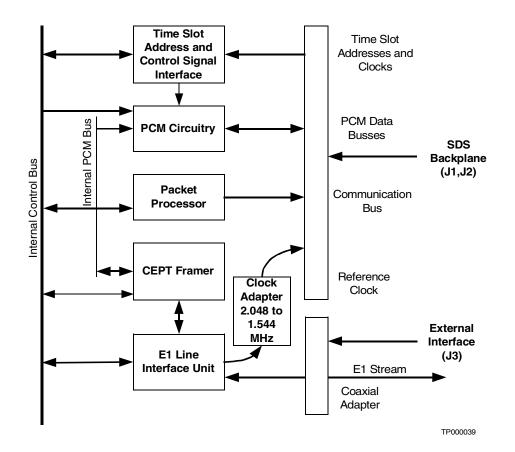

| Figure 3: Pinout Diagram of E1/E1-PRI Adapters<br>Figure 4: E1-CAS Card Jumper Locations<br>Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 1   | : Block Diagram of E1-CAS Card                             | 2  |

| Figure 4: E1-CAS Card Jumper Locations Earth/Loop Connect Trunk Card (ECT/LCT) Figure 1: Block Diagram Of ECT/LCT Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector Figure 3: ECT/LCT Jumper & PROM Locations International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 2   | : CAS Multiframe Format                                    | 6  |

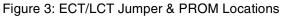

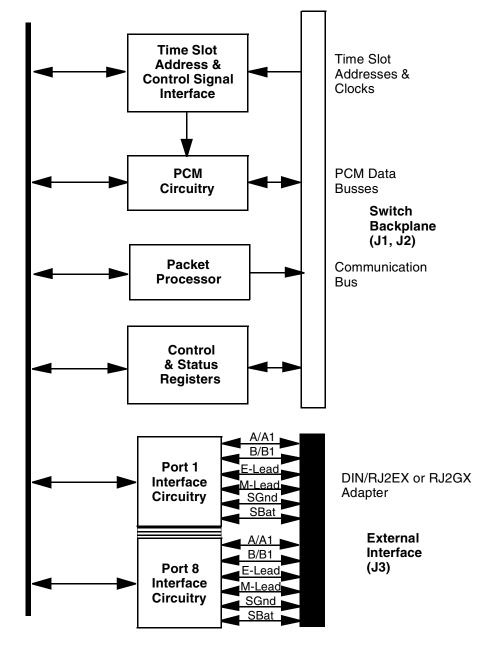

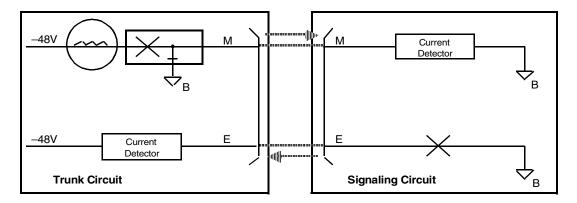

| Earth/Loop Connect Trunk Card<br>(ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 3   | : Pinout Diagram of E1/E1-PRI Adapters                     | 12 |

| (ECT/LCT)<br>Figure 1: Block Diagram Of ECT/LCT<br>Figure 2: Pin-Out Diagram Of DIN–RJ21X Connector<br>Figure 3: ECT/LCT Jumper & PROM Locations<br>International E+M Trunk Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 4   | : E1-CAS Card Jumper Locations                             | 13 |